# Freescale Semiconductor, Inc.

用户指南

Document Number: Rev. 0, 09/2014

# 飞思卡尔单片机快速上手指南

作者: 飞思卡尔半导体IMM FAE团队

飞思卡尔半导体是全球领先的单片机供应商, 其单片机产品包含多种内核,有数百个系列。 为支持用户使用这些产品,飞思卡尔提供了丰富的网站资源、文档及软硬件工具,另外,我们还有众多的第三方合作伙伴及公共平台的 支持。对于不熟悉飞思卡尔产品和网站的初学 者来说,了解和使用这些资源这无疑是一个令 人望而生畏的浩瀚工程。本指南的目的,就是 给初学者提供一个指导,让他们不被这些海量 信息淹没;用户根据本指导提供的操作步骤, 能迅速找到所需的资源,了解如何使用相关的 工具。

在本指南中,我们以飞思卡尔的新一代Kinetis 单片机K22系列为例,介绍了如何获取与之相 关的资源,如何对其进行软硬件设计和开发。 实际上,这些方法也适用于其它的单片机系列。 当然,对于其它有较多不同之处的产品,我们 也会继续推出相应的文档,供广大用户参考。

#### 景目

| 1 | 如何获取技术资料与支持             | 2  |

|---|-------------------------|----|

| 2 | 如何选择产品、申请样片及购买少量芯片和开发工具 | 9  |

| 3 | 飞思卡尔单片机的开发环境、开发工具和生态系统  | 22 |

| 4 | 如何阅读飞思卡尔的技术文档           | 45 |

| 5 | 飞思卡尔单片机硬件设计指南           | 55 |

| 6 | 飞思卡尔单片机软件开发指南           | 67 |

# 如何获取技术资料与支持

#### 1.1 概述

当用户使用飞思卡尔单片机芯片时,如何获取芯片的数据手册(Datasheet)、参考设计(Reference Manual)和官方例程等资源呢?另外当用户遇到了技术问题该如何获得帮助和解答呢?这里以 Kinetis的K22系列芯片为例为大家介绍如何解决这些问题。

## 1.2 如何查找芯片的技术资料

射频

1. 飞思卡尔芯片的资料全都可以在飞思卡尔的官网上免费下载。进入飞思卡尔官网 www.freescale.com, 如果您习惯使用中文,点击右上角"Select language"下的"中文", 选择显示中文,如图1所示,用户以后再进入该网站时,它就会自动默认为中文显示。

图 1 飞思卡尔网站中文语言选择

2. 然后选择 "产品" → "微控制器" → "Kinetis ARM ® MCU", 如图 2所示。

图 2 选择 Kinetis ARM MCU

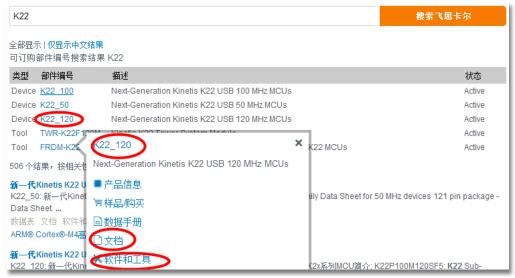

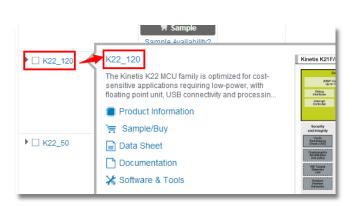

3. 在Kinetis微控制器/单片机界面中,在左下方选择K22 120 (120表示主频为120M),如图 3所示。点击此链接,可进入K22 120的产品页面。

图 3 选择 K22\_120

图 4 K22\_120 资源集合

4. 如图 3 所示,进入产品页面之后,可以看到这里包含很多资源。在"文档"栏目中能找到芯片的数据。 参考手册、应用笔记、用户指南等;在"软件和工具"栏目中能找到芯片使用的仿真调试器、评估开发板、软件开发工具等。您可以根据需要进行相关资源的下载。

另外您也可以通过飞思卡尔官方网站的搜索功能进行查找。方法是先进入官网<u>www.freescale.com</u>, 在右上角的搜索框中输入K22,然后点击搜索图标或按Enter键进行搜索,如图 5所示。

图 5 搜索关键字/芯片型号

搜索后的结果如图 6所示,在这里同样可以获取您需要的相关资源。

图 6 搜索结果

另外,在飞思卡尔官网上有一些针对某些应用领域的参考设计,这些参考设计可以帮助您快速进行产品开发。以电表的设计为例,在飞思卡尔官网上点击"应用"→"工业"→"智能电网与智能仪表",如图 7所示。之后在对应页面可以找到相关的参考设计,如图 8所示。

图 7 智能电网与智能电表

图 8 参考设计

# 1.3 如何得到技术支持

当您在使用飞思卡尔芯片的过程中遇到问题时,您可以通过以下的途径得到支持: TIC、在线论坛和当地FAE。

#### 1.3.1 技术信息中心(TIC)

通过TIC,您可以提交技术服务请求SR(支持使用中文),之后会有专业的技术支持工程师为您在线解答。TIC工程师都是飞思卡尔的资深工程师,他们分布在飞思卡尔全球各地的机构中,专门负责解答客户通过网络提交的问题。每个服务请求完成之后,都会向客户发送满意度调查表。提交SR的具体操作步骤如下:

1. 进入飞思卡尔官网<u>www.freescale.com</u>,点击"支持服务与网络社区"→"销售与技术支持",如图 9所示。进入"销售与支持"页面,点击"创建服务请求",如图 10所示。

图 9 销售与技术支持

图 10 创建服务请求

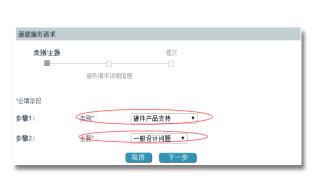

2. 选择技术服务类别和主题,如图 11所示。

新建服务请求

类别主题

P品问题

服务请求详细信息

产品问题

提交

请选择器件

请在以下器件中选择一个与您的技术问题有关的器件

您已选中▶微控制器▶ Kinetis MCU(基于Cortex-M内核)▶ K系列▶ K2x USB MCU▶ K22\_50

设备类型

由.模拟技术与电源管理

由.微控制器

由. Kinetis MCU(基于Cortex-M内核)

图 11 技术类别与主题

图 12 选择器件

3. 选择器件,如图 11所示。

之所以要将问题进行分类,是为了将问题细化归类,从而有利于我们后台的TIC工程师进行问题分拣,进而能找到对所提交问题最有经验的工程师来解答。

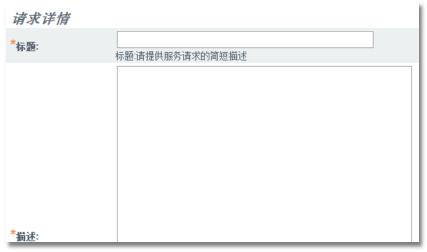

4. 录入问题描述,可以添加附件,如图 13所示。这里您既可以输入中文,也可以输入英文, 我们鼓励用户的描述能尽可能的详细和清楚。

图 13 问题描述

5. 最后提交技术服务请求(需要在飞思卡尔官网注册账号并登陆)。用户可以随时查看SR(服务请求)的处理状态。正常情况下,我们的TIC工程师会在24小时内回复到用户注册的邮箱。之后用户就可以直接通过回复邮件的方式直接跟这个工程师沟通,而不需要再去重新提交问题,直到问题解决。如果是新的问题,则需要重新提交一次。在用户的问题解决完之后,系统会自动发送一份满意度调查表到用户的邮箱,用户可以给本次服务作一个满意度评估。飞思卡尔也会根据评估来提高服务质量。

#### 1.3.2 在线论坛

论坛包括两大类,一是飞思卡尔自己的官方论坛: https://community.freescale.com/welcome。

在这里用户可以先搜索是否有人曾遇到过类似的问题,或者创建自己的问题。提问时可以用中文,但最好用英文,这样就可以有全世界的技术人员进行解答,如图 14所示。

图 14 Community 搜索与提出问题

还有一类是飞思卡尔第三方中文论坛,主要包括以下三个:

• 与非网: www.freescaleic.org/bbs/

• 21ic: <a href="http://bbs.21ic.com/iclist-192-1.html">http://bbs.21ic.com/iclist-192-1.html</a>

• 阿莫论坛: www.amobbs.com/forum-9936-1.html

它们的二维码如下:

与非网

21ic

阿莫论坛

无论是飞思卡尔自己的论坛还是第三方的论坛,都有飞思卡尔的FAE和专门支持论坛的TIC工程师支持和回复。这里以与非网为例,可以看到版主均是飞思卡尔的工程师,而且数量很多。

# 【飞思卡尔FAE线上技术支持】(发帖数: 56) 版主: FSL\_FAE\_MARK FSL\_FAE\_Frank\_Fu FSL\_TICS\_MAHUI FSL\_TICS\_Kan FSL\_TICS\_TIANZHE FSL\_FAE\_YDW FSL\_FAE\_Hanson FSL\_FAE\_ConstYu FSL\_FAE\_Strong FSL\_TICS\_XWP FSL\_TICS\_ZP FSL\_TICS\_Robin FSL\_FAE\_JiCheng FSL\_TICS\_ZJJ

图 15 第三方论坛的飞思卡尔工程师版主

FSL FAE SU FSL FAE River 小士 FSL FAE LiKe

#### 1.3.3 通过FAE得到技术支持

另外您还可以与代理商FAE或者飞思卡尔原厂FAE进行联系以获取相关的技术支持,建议您先与相应的代理商FAE联系。

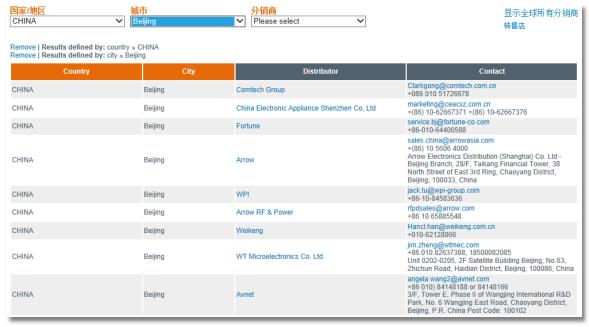

飞思卡尔目前有六家代理商,分别为Arrow(艾睿电子)、Avnet(安富利)、WT(文晔科技)、Weikeng(威健国际)、Comtech(科通)和CEAC(中电器材)。

可以通过点击"样品与购买"→"从分销商处购买",查看代理商的相关信息,如图 16所示。

图 16 进入代理商信息页面

进入界面之后,选择国家和城市,就可以查看到相应的代理商联系方式,如图 17所示。

图 17 代理商信息

#### 注意

有些代理商现在已经退出了,如Fortune和WPI。这些信息在网站上暂时还没有更新,用户需留意。

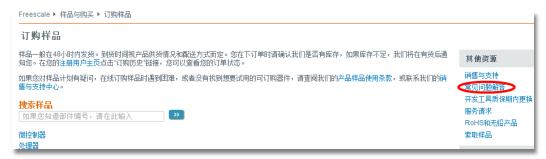

## 1.4 如何查找中文文档

飞思卡尔为中国用户提供了很多中文文档,而且更多的中文文档正在陆续发布。为方便用户,部分使用频率比较高的中文文档被整理在一起。用户点击"支持服务与网络社区"→"文档"即可看到,如图 18所示。

图 18 飞思卡尔网站的中文文档

# 2 如何选择产品、申请样片及购买少量芯片和开发工具

# 2.1 概述

本章将介绍如何确定飞思卡尔单片机的具体型号,如何申请样片、购买芯片及开发工具。本章仍以Kinetis K22系列MCU为例进行说明。

#### 2.2 芯片选型

飞思卡尔单片机的种类非常多,那么该如何获取合适的芯片呢?飞思卡尔提供了多种不同的方法和工具来帮助用户找到合适的产品。根据对飞思卡尔产品的了解程度和查找目的的不同,用户可以采用不同的方法进行选择。

## 2.2.1 主页产品查找

如果用户已经知道要查找的产品的基本信息,例如已经知道要找带USB功能的K22系列的MCU,但是需要找到一个具体的芯片型号,最常用的方法是在主页进行查找,具体步骤如下:

1. 进入飞思卡尔官网www.freescale.com,选择"产品"→"微控制器"→"Kinetis ARM® MCU",之后就会进入到Kinetis微控制器/单片机主页,如图 19所示。

图 19 Kinetis 微控制器/单片机主页

2. 在主页的左下方Kinetis微控制器处,可以进入到每个系列MCU的各个子系列,在这里我们选择K22 100,如图 20所示。这里100表示芯片的主频为100MHz。

图 20 选择 K22\_100 子系列

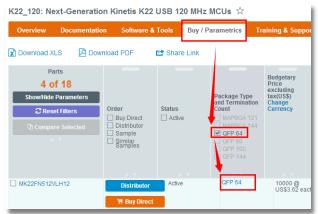

3. 进入K22\_100主页之后,选择"购买/参数",就会出现该系列所有芯片的参数信息,如封装形式,管脚数量,内存大小等,可通过这些参数选择最合适的芯片,如图 21所示。

图 21 K22\_100 购买/参数

#### 2.2.2 辅助选型工具

如果用户并不清楚需要查找的芯片基本信息,飞思卡尔还提供了一些辅助的选型工具来帮助用户进行芯片的选型,分别介绍如下。

#### 2.2.2.1 参数选型工具

如果用户知道需要什么内核的产品,则可以通过"参数选型工具"来辅助进行芯片选型。步骤如下:

1. 进入飞思卡尔官网www.freescale.com,点击页面上方的"参数选型工具"。如图 22所示。

图 22 参数选型工具

2. 选择"微控制器"→ "Kinetis MCU(基于Cortex-M内核)",如图 23所示。

图 23 选择 Kinetis MCU

3. 在器件类型中, 我们选择"K2x USB MCU", 如图 24所示。

图 24 选择器件类型

4. 之后您可以进行多种操作,以辅助您选取到合适的芯片。比如您可以通过"显示/隐藏"参数来调整页面的参数显示类型,如图 25所示。您还可以通过调整参数的范围来进行芯片的选取,如图 26所示。

图 25 显示/隐藏参数

图 26 调整参数范围

#### 2.2.2.2 选型神器Cross Check

您还可以通过选芯神器Cross Check(目前最新版本为V3. 来帮助您快速找到合适的飞思卡尔芯片,该软件具有以下功能:

- 根据输入的芯片型号或参数特性来显示飞思卡尔相关器件的预算价,并能够订购样品或购买器件。

- 根据用户输入的竞争对手的芯片型号,给出4款最适合的飞思卡尔器件。

该软件的下载地址为:

http://www.freescale.com/zh-Hans/webapp/sps/site/overview.jsp?nodeld=05D8D7194A&uc=true&lang\_cd=zh-Hans/ 打开该网页后,可以扫描右侧的二维码进行下载手机应用软件,如图 27所示。

图 27 Cross Check 软件下载

您也可以使用网页版的工具,方法是先登陆飞思卡尔官方网站,在"我的账号"→"安全应用"下,可以找到选型神器的应用,包括"部件预算价"和"竞争对手交叉参考"两个工具,如图 28 所示。图 29和图 30是两个工具的使用界面。

图 28 部件预算价和竞争对手交叉参考

图 29 部件预算价工具

图 30 竞争对手交叉参考工具

#### 注意

对于"竞争对手交叉参考",可以不用登陆就能使用,位置在"Kinetis 微控制器/单片机"主页,右侧的"辅助工具"→"交叉参考工具"以及下方的"设计资源"→"支持和专业服务"→"MCU竞争对手交叉参考"。如图 31所示。或者通过网址www.freescale.com/crosscheck进入。

图 31 竞争对手交叉参考工具

#### 2.2.2.3 解决方案顾问(Solution Advisor)

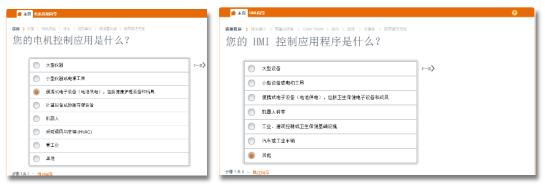

飞思卡尔解决方案顾问是一款基于Web的互动式应用向导和动态产品选型工具。如果用户完全不知道要使用哪个芯片,则可以通过这个工具来查找合适的芯片。使用步骤如下:

1. 通过<a href="http://freescale.transim.com/solutionadvisor/LandingPage.aspx">http://freescale.transim.com/solutionadvisor/LandingPage.aspx</a>进入到 "Solution Advisor" 的主页,如图 32所示:

图 32 "Solution Advisor"主页

2. 选择"产品选择器",如图 33所示。在这里按照提示的先后步骤您可以快速找到最合适的 处理器和工具。

图 33 产品选择器

3. 此工具还提供了电机控制向导,如图 34所示。它可以帮助您快速找到最合适的电机控制解决方案。

图 34 电机控制向导

图 35 HMI 向导

- 4. 您还可以使用HMI向导,如图 34所示。它可以帮助您快速找到最合适的HMI解决方案。

- 2.3 申请免费样片与购买芯片

# 2.3.1 申请免费样片

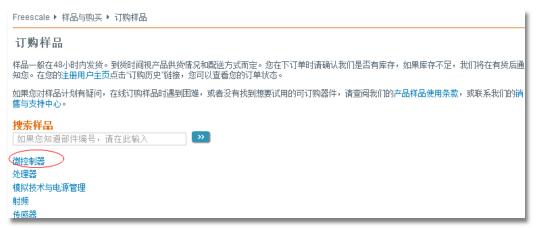

1. 在官网点击"样品与购买"→"索取样品",可以进行免费样片的申请,如图 36所示。

图 36 免费样片申请

2. 选择微控制器,以K22举例,经过检索可以找到K22的相关样品,或者您可以直接通过"微控制器"→"Kinetis"→"K系列"→"K2x"→"K22"的方式找到该芯片,检索界面如图 37所示。

图 37 检索样品

3. 检索到样片之后,点击黄色的"样品"按钮。如图 38所示。

图 38 选择样品

#### 注意

我们的样品在一定数量内为免费样品,并且快递费用全免。关于样片 具体申请的个数及费用等相关信息,可以在"常见问题解答"中得到 相关解释。如图 39所示。

图 39 常见问题解答

#### 2.3.2 如何购买少量芯片

#### 2.3.2.1 在飞思卡尔官网上购买

- 1. 在飞思卡尔官网上注册。如果您已经是会员,请登录网站。

- 2. 搜索器件。找到可订购器件的"直接购买"按钮,该图标位于器件号右侧。如图 40所示。

图 40 直接购买图标

3. 点击"直接购买"按钮图标,将产品添加到您的购物车中。当您将产品添加到购物车后, 您可以更新您的购物车,继续购物或结帐。如图 41所示。

图 41 购物车

目前,我们支持支付宝、VISA和Master卡来进行网上直接在线支付。但是客户需要自己负责清关。(手续并不麻烦,但是在海关要求的情况下需要客户自己处理。因为是小批量订单,而且我们不知道客户的具体用途,所以需要客户自己清关。)

4. 您在下订单之后,将会收到一封确认电子邮件。您可以对已注册用户主页进行个性化定制, 随时跟踪订单情况。(到货时间视产品供货情况和配送方式而定。)

# 2.3.2.2 第三方供应商小批量芯片购买

除了飞思卡尔官网之外,客户还可以用过以下与飞思卡尔有官方合作的芯片在线销售公司来购买小批量芯片:

- Element 14: http://www.element 14.com/community/welcome

- E络盟: <a href="http://cn.element14.com/">http://cn.element14.com/</a>

- 周立功: http://www.zlgmcu.com/

- DigiKey: http://www.digikey.com/

- Mouser: http://eu.mouser.com/

#### 2.3.3 购买开发板

当您需要购买开发板时,可以在飞思卡尔官网上进行购买,步骤如下:

1. 点击 MCU 界面的软件与工具,在硬件开发工具中查看该系列 MCU 有哪些开发板。这里还以 K22 举例说明,如图 42 和图 43 所示。

图 42 软件与工具

图 43 硬件开发工具

2. 点击相应的开发板之后,可以进入这个开发板的主页,这里以FRDM-K22F为例。可以看到相关的各种资源,在"文档"栏目中能找到开发板的用户指南等,在"下载"栏目中能找到开发板的原理图、Sample code、快速开发包等;选择"购买/规格"就可以进行购买。如图 44所示。

图 44 购买开发板

另外从飞思卡尔的第三方合作伙伴,如uCDragon(优龙科技)、Manley(万利电子)、周立功和 lierda(利尔达一),同样可以购买到他们为飞思卡尔芯片定制的开发板。

他们的网址分别为:

• 优龙科技: <a href="http://www.ucdragon.cn">http://www.ucdragon.cn</a>

• 万利电子: <a href="http://www.manley.com.cn">http://www.manley.com.cn</a>

● 周立功: <a href="http://www.zlgmcu.com">http://www.zlgmcu.com</a>

• 利尔达: http://www.lierda.com

以优龙科技为例,首先进入官网<u>http://www.ucdragon.cn</u>,在"产品分类"中的"ARM开发板"中可以找到飞思卡尔相关的开发板。如图 45所示。

图 45 uCdragon freescale 开发板

点击相应的开发板之后,可以获得该开发板的信息,通过页面左下方的联系方式,用户可以购买 到该开发板,如图 46所示。

图 46 优龙的销售联系方式

# 3 飞思卡尔单片机的开发环境、开发工具和生态系统

#### 3.1 概述

在根据需求完成选型之后,用户应开始了解相关的开发环境、开发工具和生态系统,评估飞思卡尔提供的工具和资源是否能够满足用户的开发需要。本章节将会介绍集成开发环境(IDE)、评估板(EVM)、调试器(Debugger)、参考代码与设计(Sample code with documents & Existing Reference Design)以及生态系统(ecosystem)。希望本章节的内容能让用户快速准确地找到相关资源来完成这一过程。

# 3.2 集成开发环境(IDE)

集成开发环境就是针对可编程器件的集编辑、编译和调试功能于一体的开发调试工具。以Kinetis 系列MCU为例,通用的IDE均可支持,例如IAR、Keil等。另外飞思卡尔也有自己的IDE,分别是KDS(Kinetis Development Studio)和CodeWarrior,本节将会主要介绍这两个工具及内嵌在这两个IDE中的代码生成工具"处理器专家"(Process Expert)。

# 3.2.1 KDS (Kinetis Design Studio)

KDS是飞思卡尔在2014年刚刚推出的专门用于支持Kinetis系列MCU的一款集成开发环境软件,能够提供代码编辑到调试的完整功能。KDS的特点如下:

- 支持目前Kinetis全系列的产品,并将不断更新对新产品的支持;

- 开源免费, 且不受软件代码大小的限制(提醒: Keil、IAR等IDE均需要收费);

- 支持在32/64位的Windows 7/8的操作系统上运行;

- 使用Elipse界面风格,并且支持其他可下载的插件,如Processor Expert;

- 支持SEGGER J-Link/P&E USB Multilink Universal/CMSIS-DAP/OpenSDA等调试接口;

- 专门为Kinetis系列MCU开发,因此具有内核编译器小、响应速度快的优势。

#### 3.2.1.1 KDS软件下载与安装

目前KDS的最新版本是V1.1.1,以下描述均以该版本为例。软件与相关说明文档的下载路径如下:

- 软件: 中文首页->软件和工具->软件中心->IDE-调试、编译与构建工具->微控制器-Kinetis Design Studio->下载

- 文档: 中文首页->软件和工具->软件中心->IDE-调试、编译与构建工具->微控制器-Kinetis Design Studio->文档

在Windows系统上安装KDS很简单,只需双击KDS-v1.1.0.exe,根据向导即可完成。另外,飞思卡尔还提供了一个工具,叫做Kinetis软件开发套件(KSDK),它可以嵌入KDS中使用,为用户提供丰富的外设驱动代码、协议栈代码、中间件代码和示例代码。关于KSDK的详细介绍,请参见飞思卡尔单片机软件开发指南的内容。

在完成KDS的安装后,如果需要在KDS中嵌入KSDK,则还要下载和安装KSDK软件包,软件与文档的下载路径如下:

- 软件: 中文首页->软件和工具->软件中心->中间件->用于 Kinetis MCU 的软件开发套件->下载

- 文档: 中文首页->软件和工具->软件中心->中间件->用于 Kinetis MCU 的软件开发套件->文档

在下载安装KSDK后,要嵌入KDS中使用要完成以下步骤:

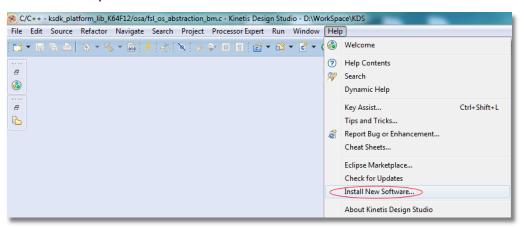

1. 启动KDS并在"Help"选项中选择"Intall New Software"。

图 47 在 KDS 中安装 KSDK 步骤一

2. 在 "Available Software"的窗口中,点击"Add"并找到KSDK安装目录中的.zip文件,点击"OK"。

图 48 在 KDS 中安装 KSDK 步骤二

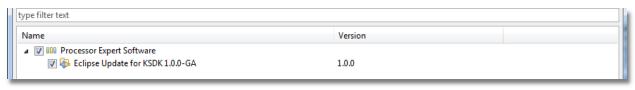

3. 找到文件位置后,在"the Processor Expert Software category"的项目下显示有"Eclipse Update for KSDK";在勾选框内打勾,并点击"Next"并完成安装。

图 49 在 KDS 中安装 KSDK 步骤三

另外,如果需要在 KDS 中使用 Processor Expert,还需要安装一个更新补丁。该补丁名为 <u>Processor Expert for KDS 1.1-Updata 1</u>,下载路径与 KSDK 相同,安装方法也与安装 KSDK 相同,可参照上述步骤进行操作。

#### 3.2.1.2 在KDS中新建工程与导入已有工程

在KDS中新建一个工程可参考以下步骤:

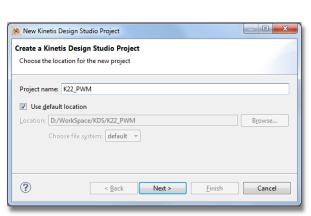

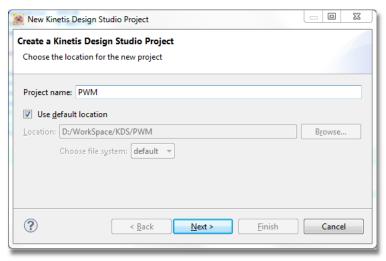

- 1. 在打开KDS后,选择新建工程"File"→"New"→"Kinetis Design Studio Project"。

- 2. 输入工程名,并在选择工程的存储位置后,点击"Next"。

图 50 在 KDS 中新建工程步骤二

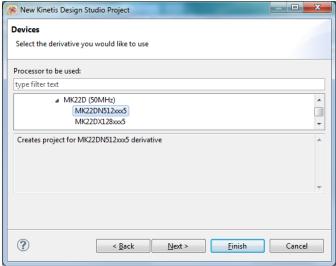

图 51 在 KDS 中新建工程步骤三

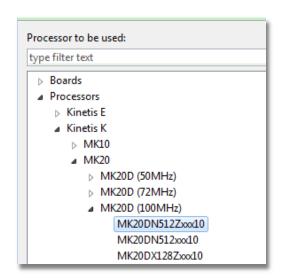

- 3. 选择需要评估的芯片型,点击"Next"。

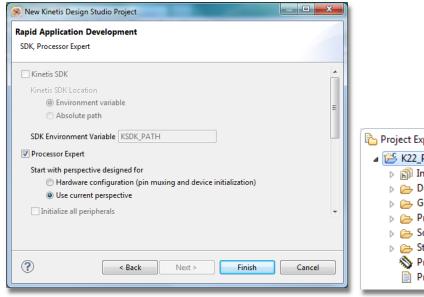

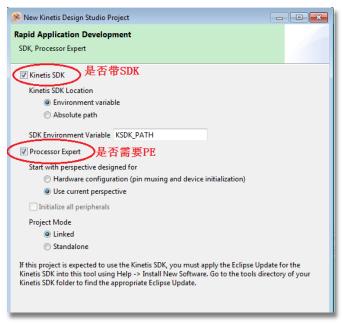

- 4. 在"Rapid Application Development"中,可以在新建工程中加入Process Expert和KSDK来简 化底层驱动代码的编写工作。Processor Expert已包含在KDS中,但加入KSDK需要按照KDS软 件下载与安装中的步骤手动安装。

陷 Project Explorer 🔀 ▶ 🛍 Includes Documentation > 🗁 Generated\_Code Project\_Settings Sources ProcessorExpert.pe ProjectInfo.xml

图 53 在 KDS 中新建工程步骤五

- 5. 在完成上述配置后,点击 "Finish"可以看到如图 52所示的 "Project Explorer"界面。

- 6. 在工程中,可以通过右击项目名选择"New"→"Source File"来新建文件,也可以通过拖 拽功能将已有的源文件、头文件和目录等加入到工程中。

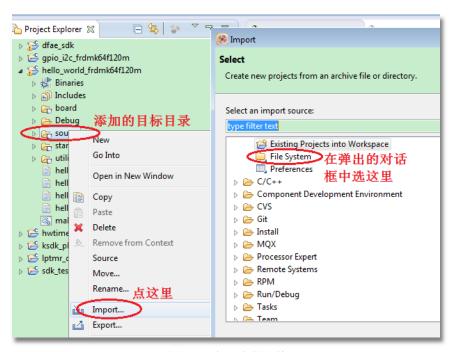

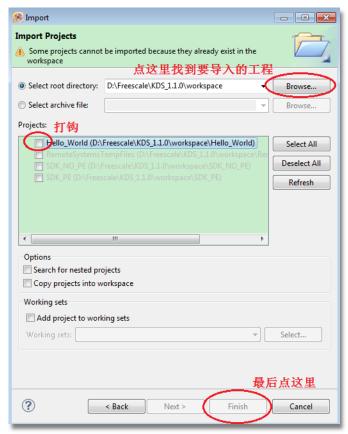

导入已有工程可参考以下步骤:

- 1. 在打开KDS后,选择"File"→"Import"。

- 2. 在"Import"页中,选择"Existing Projects into Workspace"并点击"Next"。

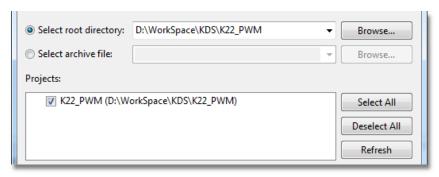

- 3. 在"Import Projects"页中,选择"Select root directory"并点击"Browse"来选择已有工程的目标文件夹,选好后点击"OK"。

图 54 在 KDS 中导入已有工程

4. 在 "Projects" 框中会列举出目标文件夹中所有的工程,在需要导入的工程前的选项框内打 勾,并点击 "Finish"。

## 3.2.1.3 编译与调试

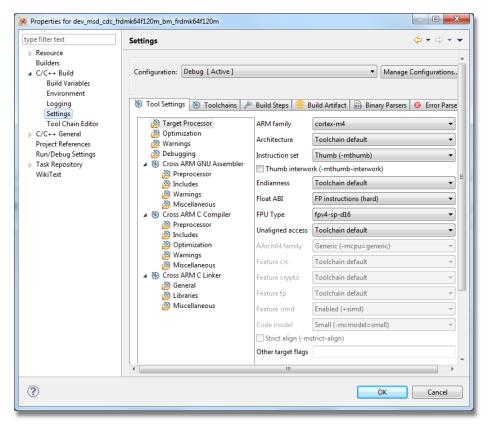

在开始编译程序之前,需要预先配置好工程的一些编译参数。右击要编译的Project并选择 "Properties",在"Proporties for example"页中可以看到工程的所有参数。点击展开"C/C++Build" 后在Settings中可以看到跟编译有关的参数,默认的参数一般无需修改,如需修改,请参照说明文档。

图 55 在 KDS 中配置编译参数

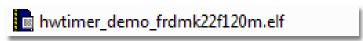

在点击编译 <sup>5</sup> 图标后,在相应的工程文件中看到编译生成的.elf文件,如图 56所示。

图 56 编译后生成的可下载文件

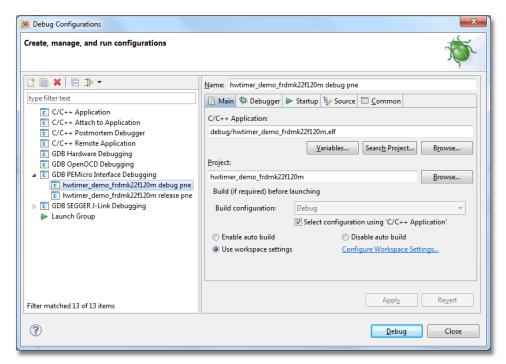

在开始下载之前,需要先配置相关调试参数,如选择调试接口等。右击需要调试的工程并选择 "Debug As" → "Debug Configurations"进入"Debug"配置页面,如图 57所示。也可以通过点击调试按键右侧的向下箭头来进入"Debug"配置页面。在"Main"选项卡中,需保证"C/C++ Application"一栏中所选的.elf文件为需要调试的工程对应产生的编译文件。对于"Debugger"和"Startup"两栏,根据调试器的不同,需要进行不同的配置,如图 57所示。这部分内容会在调试工具(Debugger)中作具体介绍。

图 57 在 KDS 中调试配置

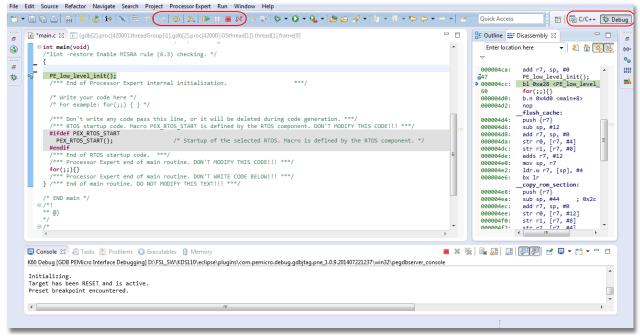

图 58 在 KDS 中进行调试

配置完成后,将目标板与PC机通过USB线和相关调试器连接起来,依次点击"Apply"和"Debug"两个按键进入"Debug Perspective",如图 58所示,可以程序已暂停在main()函数的初始处。这样就可以实际调试程序了。表 1列出了工具条中各按键的主要作用。

#### 表1在KDS中调试按键功能

| 按键        | 说明       | 按键       | 说明      |

|-----------|----------|----------|---------|

| <b>○▶</b> | 开始/继续执行  | _@       | 单步返回函数  |

| 00        | 暂停执行     |          | 复位      |

| i→        | 使能汇编单步执行 | 27       | 断开仿真器   |

| <u>♣</u>  | 单步执行     |          | 结束调试    |

| <b>₹</b>  | 单步进入函数   | <u>*</u> | 开始下载与调试 |

#### 3.2.1.4 下载

在程序调试完成后,需要将调试好的程序下载到FLASH中。

点击下载按钮 , 进入 "Flash Configurations"界面。配置可参考编译与调试中的要求相同。在 完成配置后,依次选择"Apply"和"Flash",等待程序下载完成后,重新上电或手动复位后程 序开始运行。

# 3.2.2 CodeWarrior集成开发环境

CodeWarrior(简写为CW)原是Metroworks公司的产品,后来该公司被飞思卡尔收购,因此CW也就成为了飞思卡尔自己的IDE系统,目前已在业内使用多年。从10.0版本以后,CW开始使用Eclipse界面,能够支持不同架构的芯片,包括ColdFire、ColdFire+、DSC、Kinetis、PowerPC、Qorivva、RS08、S08和S12Z等。

目前针对飞思卡尔单片机的CW的最新版本是CodeWarrior for Microcontrollers v10.6。另外根据客户的用途和需求不同分为评估版、基础版、标准版和专业版,其中评估版是免费的,其支持代码和数据大小也是有限制的。以Kinetis系列MCU为例,K系列的限制为128KB,E/L/M/V系列的限制为64KB,如超出限制,则需要申请更高级的版本。

另外需要提醒的是,对于v10.6以后的版本,CodeWarrior不会再支持其后发布的Kinetis系列的产品,因此对于使用Kinetis新产品的用户,需要将软件平台逐步转移到其他IDE上,由于CodeWarrior与KDS所建立的工程兼容,因此推荐使用KDS完成IDE平台的切换。

CodeWarrior软件的安装包和相关文档的下载路径为:

- 软件: 飞思卡尔中文首页->软件和工具->软件中心->IDE-调试、编译与构建工具->微控制器->CodeWarrior for MCUs->下载

- 文档: <u>飞思卡尔中文首页->软件和工具->软件中心->IDE-调试、编译与构建工具->微控制器->CodeWarrior for MCUs->文档</u>

在支持的调试接口、新建工程与导入工程、调试与编译等方面,CodeWarrior与KDS基本相同,此处就不作介绍,具体细节可以参照相关说明文档。

# 3.2.3 处理器专家(Processor Expert)

PE(Process Expert)是一款支持Kinetis、Coldfire等多种不同内核的MCU的快速应用开发软件。该软件以图形化界面的方式快速配置MCU的内核及外设,生成相应的初始化及应用代码,省去手动编写底层驱动代码的繁复工作,从而大大提高了软件工程师的工作效率。其生成的代码可以支持KDS、CodeWarrior、IAR和Keil等多种IDE;另外,PE还以嵌入到基于Eclipse架构的IDE中,例如在KDS和CodeWarrior,可以直接使用嵌入的PE功能,PE所产生的代码将自动放置在相关工程下,然后在此基础上修改主程序就可以进行编译和调试。

KDS和CodeWarrior这两种IDE安装后都带有内置的PE,无需再额外安装。因此其安装过程就不再介绍。

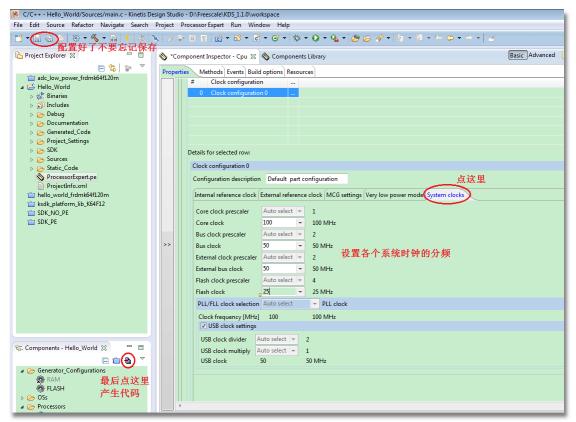

#### 3.2.3.1 新建基于PE的工程

下面以Kinetis K22为例,创建一个使用PE的KDS工程。工程所需的具体配置如下:

- 1. 首先,在KDS的选项栏中,点击"File"栏并选择"New"→"Bareboard Project"来创建一个新的工程。

- 2. 出现工程向导界面如图 59, 输入工程名并点击"Next"。

图 59 工程设置向导

- 3. 选择芯片类型,此处选择"Kinetis K Series"→"K2x Family"→"K22"。点击"Next"。

- 4. 在"Language and Build Tool Options"页中,选择C语言并点击"Next"。

- 5. 在"Rapid Appliation Developmen"页中,在"Rapid Appliation Developmen"组中,选中"Processor Expert"并点击"Finish"。至此一个包含PE功能的工程已建好,下面开始添加元件来配置所需的外设。

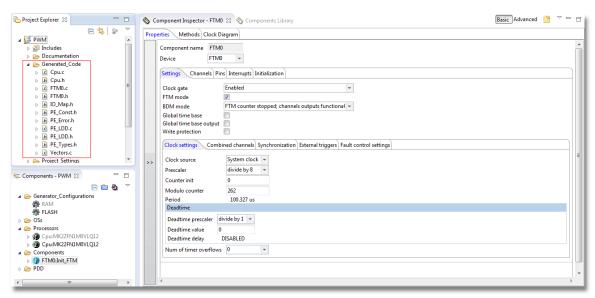

- 6. 在 "Component Library"中,找到相应组件(如FTM)并右击选择"Add to project"选项。

- 7. 点击打开添加的组件,其具体配置显示在"Component Inspector"中。

- 8. 根据所需要求进行以下配置初始化等参数。

- 9. 在配置完成后,点击图标 产生相应代码。

- 10. 所产生的代码存放在"Generated\_Code"文件夹中。可以看到FTM的相关初始化代码已自动完成,点击功能键即可编译运行。

图 60 在 KDS 中使用 Processor Expert 生成代码

# 3.3 调试工具 (Debugger)

调试工具是开发工具链中的重要一环,方便耐用的开发工具对用户非常重要。接下来就介绍三种常用的调试工具。

# 3.3.1 OpenSDA调试功能

OpenSDA是飞思卡尔自主开发的一种调试平台。在该平台中烧写不同的调试固件,可以使其兼容不同的调试工具(如实现PEMicro Segger的JLink接口等)。下面介绍如何在FRDM-K22F板上使用OpenSDA来实现Jlink调试。

- 1. 在Segger的官网上下载用于OpenSDA的固件库。下载地址为: http://www.segger.com/opensda.html。

- 2. 如果FRDM-K22板通过USB线连接到PC机上,请将其拔下。

- 3. 按住SW1键, 然后用USB线连接PC机与板上的SDA USB接口。

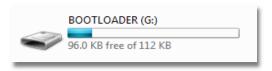

- 4. 松开 SW1键,可见板上一个LED灯在有规律地闪烁,且在PC机上能看到一个移动存储设备, 其盘符为BOOTLOADER,表示目标板进入了bootloader模式。

图 61 OpenSDA 处于 BOOTLOADER 模式下的显示

- 5. 将1中所下载的压缩包Jlink OpenSDA V2 1.zip解压缩,得到Jlink OpenSDA V2 1.bin文件。

- 6. 将上述.bin文件复制粘贴到BOOTLOADER设备中并拔下USB线。

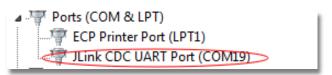

- 7. 重新插上该USB线,在设备管理器中可见到如下设备,表示固件烧写成功。

图 62 固件下载成功后设备管理器中显示

这样在IDE中就可以选择以Jlink调试下载程序了。另外OpenSDA还带有虚拟串口调试功能,串口格式如下。

波特率: 115200 bps; 1位起始位; 8位数据位; 无校验位; 1位停止位。

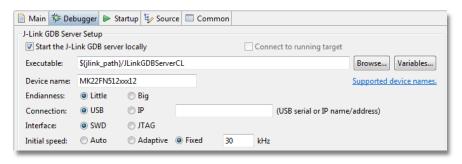

在KDS中关于使用OpenSDA设置如图 63所示。

图 63 在 KDS 中使用 Jlink 调试配置

#### 3.3.2 ILink

Jlink是SEGGER公司为支持仿真ARM 内核芯片推出的JTAG仿真器,支持Cortex M0/M1/M3/M4等内核芯片,并与KDS、CodeWarrior、IAR 和keil等多种开发环境无缝连接,使用方便。

Jlink驱动的下载地址如下: <a href="http://www.segger.com/jlink-software.html">http://www.segger.com/jlink-software.html</a>, 该驱动软件不仅提供了程序下载功能,另外J-Flash软件还可以不需要IDE软件独立地擦除与烧写程序,以及实现查看芯片的ID、RAM/FLASH大小、解锁芯片等功能。

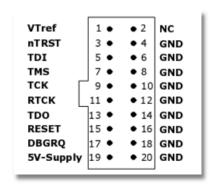

图 64为Jlink的20脚的接口图。

图 64 JLink 的标准 20 芯接口

#### 3.3.3 Multilink

P&E推出的USB Multilink Universal(FX)是一款高速一体化开发接口(USB Multilink Universal FX比 USB Multilink Universal下载速度更快),它支持Kinetis、DSC等多种MCU。因此其包含多种调试接口以匹配不同种类的MCU,图 65为支持Kinetis系列相关的三种调试接口。

| PORT B - S                                                                        | PORT F - MINI-20                                                                                                                            |  |        |  | PORT G - MINI-10 |  |                                                                            |                                                                                 |  |  |  |                           |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--------|--|------------------|--|----------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|---------------------------|

|                                                                                   | Kinetis                                                                                                                                     |  |        |  | Kinetis          |  |                                                                            |                                                                                 |  |  |  |                           |

| TVCC 1 TRST 3 TDI 5 TMS/SWD_DIO 7 TCK/SWD_CLK 9 NC 11 TDO 13 RESET 15 NC 17 NC 19 | TRST 3 • • 4 GND TDI 5 • 6 GND TMS/SWD_DIO 7 • 8 GND TCK/SWD_CLK 9 • 10 GND NC 11 • 12 GND TDO 13 • 14 GND RESET 15 • 16 GND NC 17 • 18 GND |  | TVCC 1 |  |                  |  | 4 TCK/SWD_CLK 6 TDO 8 TDI 10 RESET 12 TRACE_CLKOUT 14 TRACE_D0 16 TRACE_D1 | TVCC 1 • • 2 TMS/SWD_DIO 4 TCK/SWD_CLK GND 3 • • 6 TDO 8 TDI GND 9 • • 10 RESET |  |  |  | 4 TCK/SWD_CLK 6 TDO 8 TDI |

图 65 Multilink 用于 Kinetis 系列调试的的 3 种接口

在使用时,其连接顺序如下:

- 1. 确保目标板断电,并断开USB Multilink Universal与外部的连接。

- 2. 打开Multilink的塑料外壳,选择合适的接口将其与目标板的调试接口连接起来。

- 3. 将Multilink与PC机通过USB线相连。此时蓝灯亮。

- 4. 将目标板上电,此时黄灯亮。

在断开连接时,请先将目标板断电。使用时请遵守连接顺序,否则可能到损坏调试器。

# 3.4 评估板 (EVB)

为了缩短用户评估所选芯片以及提供硬件设计参考,飞思卡尔提供了大量的评估板,大部分评估板不仅包含了MCU的最小系统、引出的通用IO口、提供JTAG调试接口、板载调试器OpenSDA,还针对不同应用的芯片配置了USB口,触摸滑条和液晶显示等功能电路和接口。另外,这些外设的驱动程序在官网上也都一应俱全。针对Kinetis系列的评估,评估板按结构分为两种,分别是FRDM板和Tower板(塔式系统板)。一般来说FRDM板相对便宜,功能简单,而Tower板功能更加丰富。如图 66所示。

TWR-K22F12M: Kinetis K22 Tower System Module

\*\*freescale\*\*

\*\*Green Company C

图 66 FRDM 板与 Tower 板

如何根据所选的MCU型号找到最适合用于评估的EVM板是评估的第一步。下面以K22为例,用两种方法来找到所需的评估板。

1. 首先找到介绍K22的官网主页,路径为"产品"→"Kinetis ARM@ MCU"→"K系列"→"K2x USB MCU"->"K22\_120MHz"。在该主页的右栏中间可以可以看到"推荐软件和工具",其中可以看到针对K22有FRDM-K22F和TWR-K22F120M两种评估板。

#### 推荐软件和工具

TWR-K22F120M: Kinetis K22塔式系统模块 FRDM-K22F: 面向Kinetis K22 MCU的飞思卡尔Freedom开发平台 KINETIS SDK: 用于Kinetis MCU的软件开发套件

更多 🔻

#### 图 67 搜索合适的评估板的方式一

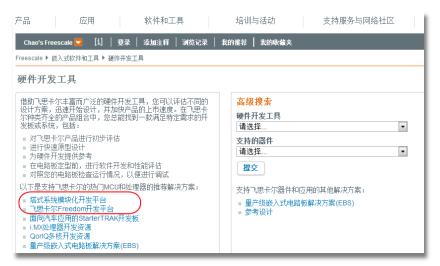

2. 在飞思卡尔的中文首页中,在"软件和工具"一栏中选择硬件开发工具。在该页面中,可以找到针对Kinetis系列的评估,有塔式系统模块化开发平台和飞思卡尔Freedom开发平台。这里选择塔式系统模块开发平台。在该页中,选择"展开MCU与处理器模块"→"Kinetis MCU模块",如图 68所示。可见所有的Tower板都已列举出,在其中总可以找到跟您所选用的型号相同或相近的评估板。

图 68 搜索合适的评估板的方式二

下面就以FRDM-K22F和TWR-K22F120M为例,介绍如何使用评估板。

#### 3.4.1 Freedom开发平台(FRDM板)

飞思卡尔Freedom开发平台是一种小型化、低功率和高性价比的评估和开发系统,十分适合针对 Kinetis MCU系列器件进行快速应用原型设计和制作演示。关于FRDM-K22F的原理图/软件包和说明文档的下载路径如下:

- 下载路径: 中文首页->产品->Kinetis ARM@M<u>CU->K系列->K2x USB MCU->K22\_120->推荐软件与工具(FRDM-K22)->下载</u>

- 文档路径: <u>中文首页->产品->Kinetis ARM@MCU->K系列->K2x USB MCU->K22 120->推荐软件与工具(FRDM-K22)->文档</u>

K22的FRDM板上基本硬件单元包括:

电源电路

板上K22F的输入5V电源可由直流插座J23或用SDA的USB口提供,输入的5V电源经过LDO输出3.3V供给板上主MCU及其他外设。在测量MCU功耗时,可将R62和R63两电阻取下,将J15线引出即可测量供给MCU的电流值以便测量功耗。

• JTAG调试电路

板上引出了SWD的调试接口,只需通过拿掉J10和J13的跳线来断开OpenSDA与主MCU的连接即可。J11的封装为标准的10脚封装(脚间距0.05")。

晶振电路

MCU上电后初始化为使用内部时钟源,可以通过修改软件选择外部时钟源,所支持的外部 主晶振的频率范围为32~40KHz以及3~32MHz。该板上的晶振频率为8MHz。另外板上的 32.768KHz的晶振用于给RTC提供时钟源。

复位电路

板上按键SW2给主芯片提供复位信号,同时SW2也与OpenSDA连接,长按SW2也可使OpenSDA进入booloader模式。

# 3.4.2 塔式系统模块化开发平台(Tower板)

飞思卡尔塔式系统是一个为8位、16位和32位微控制器设计的模块化开发平台,基于该平台,研发人员可通过开速原型技术进行样机研制。通过这个平台,用户可以采用搭积木的方式将各种功能板组合在一起,实现用户需要的各种功能。它为设计者提供了基本的模块单元,以满足微控制器进一步开发的需要。关于TWR-K22F120M的原理图/软件包和说明文档的下载路径如下:

• 下载路径: <u>中文首页->产品->Kinetis ARM@MCU->K系列->K2x USB MCU->K22</u> 120->推荐软件与工具(TWR-K22F12M)->下载

• 文档路径: <u>中文首页->产品->Kinetis ARM@MCU->K系列->K2x USB MCU->K22\_120->推荐软件与工具(TWR-K22F12M)->文档</u>

#### 3.4.3 如何申请EVB

关于如何得到相关的评估板,有两种方法.

- 1. 直接联系代理商,向其索要评估板。代理商的具体联系方法请参见通过FAE得到技术支持 小节的介绍。

- 2. 在飞思卡尔网上订购,如图 69所示。

图 69 获取评估板的方式

# 3.5 Kinetis SDK, Kinetis软件开发套件(Kinetis Software Development Studio)

Kinetis SDK是针对于Kinetis系列MCU所做的软件开发套件,又称为KSDK。它由强大的外设驱动代码库,协议栈库与示例代码库等部分组成,能够简化和加快对于Kinetis 系列MCU的应用开发。另外,Kinetis SDK是免费的工具,而且所有的硬件抽象和外设驱动软件均开放完整源代码。目前最新版本为1.0.0,支持K22、K24、K63、K64和KV3x这五种型号的MCU,随后会不断更新完善,直至能覆盖支持所有的KInetis系列MCU。

## 3.5.1 KSDK的下载与安装

以下是Kinetis SDK的下载路径及相关文档路径。

• 下载路径: <u>中文首页->软件和工具->软件中心->软件开发套件->用于Kinetis MCU的软件开发套件->下载</u>

• 文档路径: <u>中文首页->软件和工具->软件中心->软件开发套件->用于Kinetis MCU的软件开发套件->文档</u>

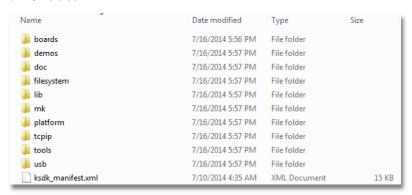

下载安装包后,只需根据向导即可完成安装。安装结束后,在安装路径中可看到如下文件夹,这些就是Kinetis SDK的主要内容。

图 70 KSDK 的完整文件

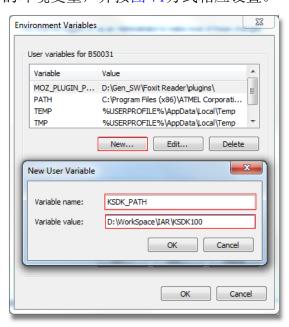

开始使用SDK之前,还需要完成以下两个步骤:

- 1. 在KDS中安装于SDK有关的eclipse插件。这一部分内容已在KDS软件下载与安装中有介绍,这里不再重复。

- 2. 设置环境变量。右击"我的电脑",依次点击"属性"→"高级系统设置"→"环境变量"可以看到如何添加新的环境变量,并按图 71方式相应设置。

图 71 设置环境变量

## 3.5.2 KSDK的结构介绍

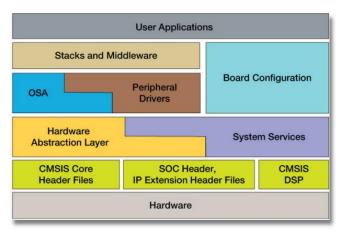

Kinetis SDK的结构如图 72所示,它包含了由底层头文件到硬件抽象和外设驱动软件、以及用户应用的完整功能。由图中不同模块的放置位置,可以看出模块之间调用与被调用的关系。下面对各个模块逐一进行介绍。

图 72 KSDK 的总体结构

#### 1. CMSIS Core Header Files/SOC Header, IP Extension Header Files/CMSIS DSP

这一层是芯片主要寄存器的地址定义,包含了与CMSIS兼容的内核定义头文件和DSP运算库。此外,还有针对不同型号芯片的外设定义头文件。所在位置路径为: "安装目录"→ "platform"→ "CMSIS"。

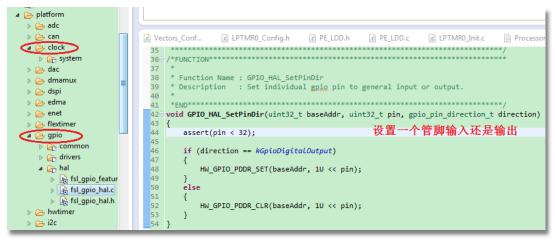

### 2. Hardware Abstraction Layer

这一模块称为硬件抽象层,简称HAL,主要负责基础模式的设置,可以理解为对底层寄存器的设置,省去了手工配置寄存器的麻烦。针对每个外设IP,都有相应的HAL文件与之对应。同时每个HAL文件也只负责与该外设IP的配置。因此,HAL层具有一定底层驱动的抽象意义,但所完成的功能相对简单。所在位置路径为:"安装目录"→"platform"→"drivers"。

#### 3. System Services

系统服务模块主要涉及一些常见的系统功能,包括中断管理、时钟管理、功耗管理和定时器管理。这一模块常与HAL配合使用,提供给上层的OSA和Peripheral Drivers模块以完成更多的功能。所在位置路径为: "安装目录"→"platform"→"system"。

#### 4. Peripheral Drivers

这一模块称为外设驱动层,简称PD。PD所完成的功能比HAL更加丰富,主要通过调用HAL和System Svevices来实现,通常PD可能调用一个以上的HAL模块。它们两者是不同的,以UART模块举例来说,UART的HAL模块只是完成了字节形式的收发功能,而其PD模块则能支持基于中断的数据流传送,或将DMA与UART配合使用。目前PD模块支持了多数的典型用法,但也没有列举完全,如UART的PD模块不支持智能卡等,这些应用会在以后更新中陆续加入。所在位置路径为: "安装目录" → "platform" → "drivers"。

#### 5. OSA

OSA的全称为Operating System Abstraction,操作系统抽象层。OSA用于设置SDK在一些操作系统上运行,当然也支持裸板模式。其包含了操作系统Kernel的大多数服务的抽象,这些操作系统包括MQX、FreeRTOS、 $\mu$ C/OS-II、 $\mu$ C/OS-III。所在位置路径为: "安装目录"  $\rightarrow$  "platform"  $\rightarrow$  "osa"。

#### 6. Stacks and Middleware

这一层包含了一些软件堆栈与协议等,如USB协议栈、TCP/IP协议栈和文件系统等。

#### 7. Board Configration

针对不同的EVM板,都有相应的SDK例程与之对应。这一模块用于配置不同EVM上的管脚复用、外设时钟给定等来实现兼容。"安装目录"→"boards"。

另外,KSDK提供了许多完整例程,可以基于EVM板运行,帮助用户学习KSDK的结构与功能, 所在位置路径为: "安装目录"→"demos"。关于如何移植KSDK来完成用户应用的开发,请参 考飞思卡尔单片机软件开发指南的介绍。

# 3.6 如何获取参考代码和参考设计

在开发应用软件时,用户不仅可能需要针对底层单个外设的驱动,还需要比较复杂功能的软件实现,甚至是一个产品或应用的整体方案。飞思卡尔有许多资源能够帮助用户在不同的开发状态下顺利完成项目。

# 3.6.1 例程代码(Sample Code)

例程代码对于MCU软件开发上手十分重要。下面给出四种找到相关代码例程的方法。

• Kinetis SDK (适合于已涵盖型号的MCU)

如上述介绍,KSDK是一种功能强大的软件开发套件,但目前还没有覆盖所有的型号。对于已经涵盖的型号,除了通过前面介绍的路径直接找到外,也可从所涵盖型号的主页下的"软件与工具"选项页中找到。

• Sample Code Package(SC,适合于尚未被SDK包含的MCU)

对于目前还没有被SDK涵盖的MCU型号,会由包含了针对某个型号的几乎所有模块驱动库的例程代码来支持。相比较SDK而言,SC的结构简单,更易于上手,但功能较弱。另外其一般被放置在对应型号的Tower板的主页中,以K64为例,路径如下:

下载路径: "K64主页" → "软件和工具" → "TWR-K64F120M" → "下载" → "软件开发工具"。

图 73 在对应 MCU 下的 sample Code

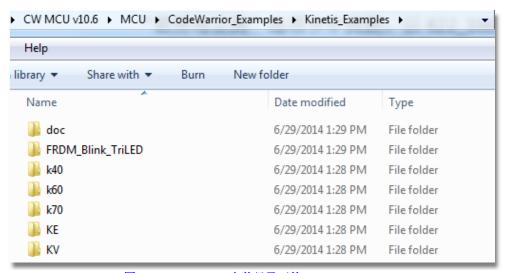

IDE安装路径下的Sample Code(适合于安装CodeWarrior等IDE的用户)

对于安装了CodeWarriord的用户,在其安装目录下也能找到针对不同系列的许多Sample Code。对于Kinetis的K系列为例,其路径如下:

"CodeWarrior的安装根目录"→"MCU"→"CodeWarrior Examples"→"Kinetis Examples"

图 74 CodeWarrior 安装目录下的 Sample Code

• 代码片段等

同样在某个型号MCU的主页中的软件开发工具中也有相应的实现某个具体功能的代码片段、引导代码等可供参考。例如:

图 75 代码片段

## 3.6.2 应用笔记

对于比较复杂功能的软件实现,例如如何在Sigma-Delata ADC上实现FFT、如何使用DMA和GPIO 来模拟PWM等,有关实现的功能原理与实现步骤都会以应用笔记的形式记录下来,而且一部分应用笔记还带有示例程序。

要准确快速地找到相关应用笔记,首先应该在所选芯片的文档中查找,对于带有例程的应用笔记,也会有图标显示。

图 76 搜索应用笔记的方式一

另外,使用文档搜索功能,能够更全面地查找到已有的AN。下面以K22为例给出搜索所有相关AN的步骤。

1. 点击首页上的搜索按键。

图 77 搜索应用笔记的方式二步骤 1

- 2. 点击左边栏中的"文档"。

- 3. 在"过滤方式"中,依次选择Kinetis MCU、K2x USB MCU。文档类型中选择"应用说明"。

图 78 搜索应用笔记的方式二步骤 2、3

### 3.6.3 参考设计

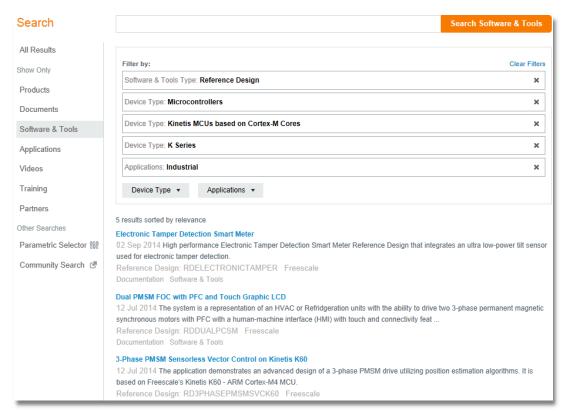

参考设计通常是针对某个应用的完整解决方案,包括硬件设计、软件代码和原理说明等。使用"软件和工具"中的高级搜索功能能够帮助您找到最合适的参考设计。下面介绍如何搜索与Kinetis 的K系列相关的DRM(Design Reference Manual)。

- 1. 点击飞思卡尔官网主页上的"软件和工具"。在中间一栏的下方找到该功能"高级搜索"。

- 2. 在软件和工具一栏中选择"参考设计"。

- 3. 在支持的器件中递进式地选择"微控制器"→"Kinetis MCU"→"K系列"。

- 4. 在应用领域中选择"工业",如图 79所示。

图 79 CodeWarrior 安装目录下的 Sample Code

在选择"提交"后,就能看到应用K系列MCU在工业领域中的参考设计。搜索到的结果如图 80所示。

图 80 参考设计的搜索结果

### 注意

由于飞思卡尔网站上的中文搜索功能不是很完善,建议用户使用英文讲行搜索。

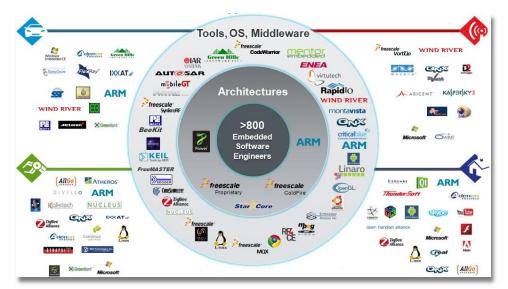

# 3.7 飞思卡尔单片机的生态系统(Ecosystem)

飞思卡尔积极与嵌入式企业合作,为方便MCU的开发与应用,建立了工具链、操作系统、中间件等不同合作联盟,此外在汽车、通信、工业与消费电子等领域企业合作,为客户提供了强大完善的生态体系。

图 81 飞思卡尔单片机的生态系统

上述不同企业根据其擅长领域的不同,为飞思卡尔提供了诸多支持,有的提供了基于 CAN 和 TCP/IP 的协议栈,有的提供了适用于物联网的 WiFi 技术,还有的提供了车载信息娱乐系统的解决方案。这些技术领先的企业对于飞思卡尔产品广泛深入的支持使得这个生态系统愈发丰富和强大,也使得用户的产品开发更加得心应手。

用户可以在飞思卡尔网站上查询到相关合作伙伴和生态合作系统的信息,如图 82所示,点击"支持服务与网络社区"→"Freescale Connect合作伙伴计划",就出现了搜索页面。

图 82 搜索飞思卡尔和合作伙伴和生态系统

# 4 如何阅读飞思卡尔的技术文档

# 4.1 概述

在嵌入式系统的研发过程中,技术文档的阅读是一个基础。对一款芯片或者一个开发平台从入门到熟悉再到深入的研究,都离不开对其相关文档的查阅。而如今不同的半导体厂家针对其自家的芯片或者开发平台都有其自己一套风格的文档体系结构,这就给一些客户的平台移植或者新手的学习入门都带来了一定程度的障碍和门槛。

本章节以飞思卡尔的Kinetis K22系列MCU为例,详细介绍了飞思卡尔公司提供的包括Datasheet、Reference Manual、User Guide、Application Note以及一些其他相关技术文档的组织结构和阅读方法,提高客户阅读文档的效率,从而进一步帮助缩短客户的研发周期。

# 4.2 数据手册(Datasheet)

与一些其他的半导体厂商不同,飞思卡尔提供的数据手册和参考手册是分开的,即两个独立的技术文档,其中数据手册(Datasheet)可以查阅到芯片相关的电气参数和封装尺寸等信息,而参考手册(Reference Manual)则主要介绍芯片具体的架构、技术细节和寄存器配置等内容,这种结构

有效地避免了单一文档的臃肿庞杂,有助于客户清晰地进行芯片选型和电气性能评估。本节主要介绍数据手册(Datasheet)的结构和阅读方法,参考手册(Reference Manual)的内容将在下一小节再做介绍。

# 4.2.1 Datasheet的命名规则

Datasheet,即芯片的数据手册,也跟芯片一样有其相应的命名规则。飞思卡尔根据芯片的家族系列、最大管脚数和主频高低对Datasheet进行了细分和命名,例如对型号为MK22FN512VLH12的芯片,与其对应的Datasheet的最新文档为K22P121M120SF7,其中K22为家族系列,P121为最大121管脚(涵盖64 Pin、100pin),M120为120M主频,SF为Sub-Family的缩写,数字7则为文档的版本号。

#### 注意

最新的版本号命名规则相较之前版本号做了些改变,加入了根据Flash 大小的分类。

# 4.2.2 Datasheet的文档结构介绍

Datasheet的内容包括Ratings、General、Peripheral Operating Requirements and Behaviors、Dimensions、Pinout和Part Identification等几个部分。其中:

- Ratings: 即额定值参数,介绍了包括温湿度额定值和芯片的工作电压电流等额定值参数。 其中特别需要注意的是,针对本文档芯片MK22FN512VLH12的最高焊接温度建议不要超过 260°C,客户在焊接操作和工艺设计的时候需要参考此部分内容。

- General: 即芯片的通用参数,既介绍了芯片的电压电流工作范围、低功耗模式下的唤醒时间和功耗参数、工作模式下的功耗/频率比和EMC特性等非开关量参数,也介绍了芯片内部时钟范围和一些外部接口的时序约束等开关量参数。

- Peripheral Operating Requirements and Behaviors: 即芯片的外设模块的工作参数,是我们做软硬件开发时最常用的部分,该部分给出了内核模块、时钟模块、内存接口、模拟外设模块和通信接口的工作参数,其中常用到的包括MCG和Oscillator时钟模块的时钟约束范围(用于倍频或者分频的配置和外部晶振的选择等)、Flash模块烧写的时间、EzPort/FlexBus的时序要求、ADC模块的采样率和有效精度、Comparator模块的带宽、DAC的有效精度和USB/SPI/I2C/UART/I2S等通信接口模块的工作参数,可以帮助客户最大程度地有效利用芯片内部的功能模块,并做相应的功能实现的预评估和测试。

- Dimensions: 芯片的封装尺寸,客户在PCB layout的过程中如果需要手工画出该芯片PCB封装的话,可以根据该部分提供的对应封装的文档序号到飞思卡尔官网搜索并下载,再参照该文档给出的封装尺寸手工画出相应芯片的封装。以MK22FN512VLH12为例,其封装为LQFP-64,Datasheet给出的对应封装的文档号为98ASS23234W。

- Pinout: 管脚分配表,K22F内部提供了丰富的外设资源,由于管脚数量的限制,其外部管脚一般需要复用成多个外设功能,除了电源管脚、晶振管脚和个别的模拟输入管脚。该管

脚复用分配表可以结合Reference Manual中的管脚复用模块寄存器配置,根据客户的实际功能需求做相应的复用功能配置。

• Part Identification: 芯片具体型号的命名规则,以MK22FN512VLH12为例,M表示量产型号,K22表示Kinetis家族K22系列,F表示带浮点运算单元FPU,N表示只有Program Flash没有FlexMemory,512表示Flash空间大小为512字节,V表示工业扩展级温度-40~105 °C,LH表示芯片封装为LQFP-64,12则表示芯片的主频为120MHz。

## 4.3 参考手册(Reference Manual)

Reference Manual,即芯片的参考手册,详细介绍了芯片的内核结构、内存映射、时钟分配、电源管理、安全加密、烧写调试、管脚复用以及所有外设模块等的技术细节,是客户开发软件必须了解也是最常需要查阅的技术手册。但是动辄上千页的参考手册,包容了如此多的技术信息,要从里面找到自己想要获取的相关资料对一个新手来说实属不易,因此有必要理清整个参考手册的结构,有针对性的攫取相关信息,掌握阅读FSL参考手册的方法。本章节以系统时钟配置、管脚复用和中断管理这三个难点也是重点的部分为例介绍飞思卡尔Reference Manual的阅读方法。

# 4.3.1 "万金油"之第三章 Chip Configuration

在介绍上述三部分的配置之前,需要重点提一下飞思卡尔参考手册非常重要的一章,即第三章 Chip Configuration,这也是飞思卡尔文档的特色之一。几乎其所有的Reference Manual中,第三章的地位一直很稳固;作为一个统领全篇的章节,其内容概述了芯片各个模块配置所需要参考的信息和功能架构并给出了一些模块更详细的配置信息和注意事项,所以我们在进行软件编程对某个外设进行配置的时候除了查看该外设相应的章节之外,第三章也是最常需要参考的一章。这里仍然以MK22FN512VLH12为例列出第三章中我们常需要参考的一些模块的配置信息:

- 1. ARM Cortex-M内核的System Tick Timer的时钟源;

- 2. 系统中断优先级的配置和中断向量表的分配:

- 3. 低功耗异步唤醒管理模块(AWIC)的唤醒源;

- 4. 极低功耗唤醒单元(LLWU)的唤醒源:

- 5. DMA模块的多路请求信号源:

- 6. 系统内存Flash和SRAM空间分配和相关注意事项:

- 7. FlexBus信号线的复用管理:

- 8. ADC模块采样通道号及硬件触发信号的分配;

- 9. 内部模拟比较器输入通道的分配;

- 10. Flex Timer的通道数、硬件触发机制和输入捕捉等参数配置;

- 11. USB模块的工作机制:

- 12. SPI模块发送和接收FIFO深度;

- 13. UART模块的中断源分配;

- 14. GPIO高驱动能力管脚的分配。

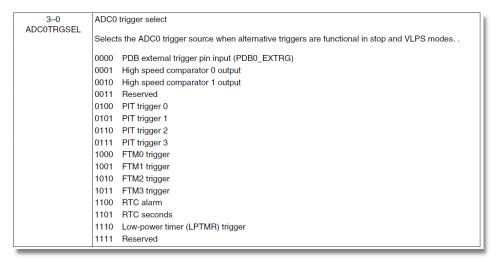

以对ADC模块进行软件配置为例,在ADC模块的章节中,ADCx\_SC1n寄存器中ADCH位即定义了ADC模块对模拟输入采样的通道号,而具体涉及到相应通道号的映射分配则可以在第三章的ADCConfiguration中找到,如图 83所示。

3.7.1.3.1.1 ADC0 Channel Assignment for 64-Pin Package

| ADC Channel (SC1n[ADCH]) | Channel | Input signal<br>(SC1n[DIFF]= 1)    | Input signal<br>(SC1n[DIFF]= 0) |

|--------------------------|---------|------------------------------------|---------------------------------|

| 00000                    | DAD0    | ADC0_DP0 and ADC0_DM01             | ADC0_DP0 <sup>2</sup>           |

| 00001                    | DAD1    | Reserved                           | Reserved                        |

| 00010                    | DAD2    | Reserved                           | Reserved                        |

| 00011                    | DAD3    | ADC0_DP3 and ADC0_DM3 <sup>3</sup> | ADC0_DP3 <sup>4</sup>           |

| 00100 <sup>5</sup>       | AD4a    | Reserved                           | Reserved                        |

| 00101 <sup>5</sup>       | AD5a    | Reserved                           | Reserved                        |

| 00110 <sup>5</sup>       | AD6a    | Reserved                           | Reserved                        |

| 00111 <sup>5</sup>       | AD7a    | Reserved                           | Reserved                        |

| 00100 <sup>5</sup>       | AD4b    | Reserved                           | ADC0_SE4b                       |

| 001015                   | AD5b    | Reserved                           | ADC0_SE5b                       |

| 00110 <sup>5</sup>       | AD6b    | Reserved                           | ADC0_SE6b                       |

图 83 ADC 通道分配图

### 4.3.2 系统时钟配置

系统时钟的配置是入门一款芯片平台的敲门砖,不同于以前的8位机和16位机简单的时钟管理,ARM平台提供了非常强大而丰富的时钟管理机制,满足其内部各个功能模块的正常运行和低功耗机制的实现,但由此带来的是复杂且繁琐的时钟配置,这让很多新手望而却步只能用拿来主义的方法去使用封装好的函数库,但是出现问题或者根据实际需要进行微调配置的时候就会常常束手无策或者拆西墙补东墙,因此通过参考手册深入地了解ARM平台的时钟管理机制之后,用户才能熟练地对系统的时钟进行配置。

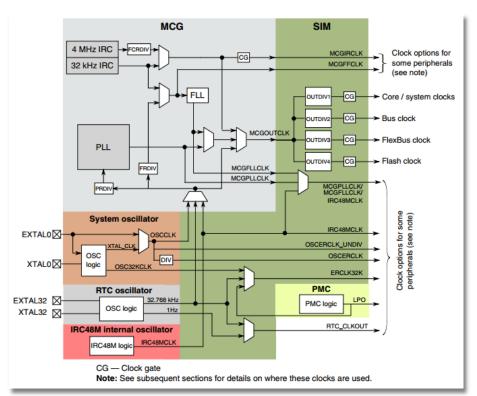

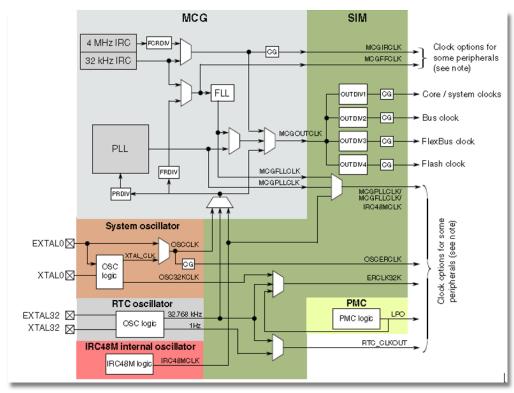

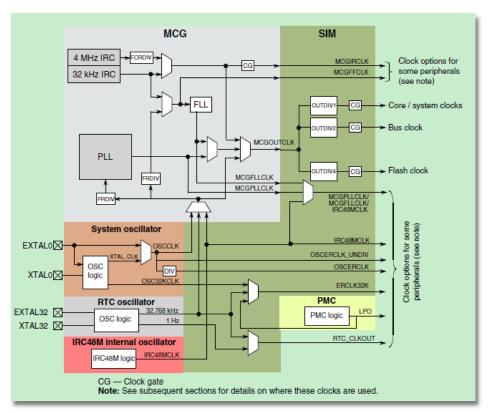

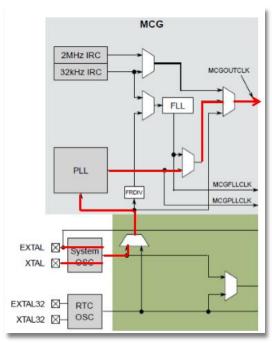

图 84 系统时钟总体框图

通常的建议是以图文结合的形式去了解和熟悉系统的时钟管理机制。如图 84所示,将 MK22FN512VLH12参考手册中"第五章 Clock Distribution"的系统时钟总体框图,拆分开来,就可以清晰的了解其平台的时钟管理机制主要是由MCG模块、SIM模块、System Oscillator模块,RTC模块、IRC48M internal oscillator和PMC这六个子模块构成。

图 85 MCG 模块内部框图

从总体到局部的角度来看,在对总体结构有了全局的认识之后,则可以通过查看上图1对应的六个子模块来深入了解其寄存器级的配置实现,以MCG子模块为例,可以在与其对应的章节里找到该模块的结构框图如图 85所示,图中给出了与System Oscillator和SIM这两个子模块的接口,对MCG内部的寄存器级的实现也给出了详细的比特位的配置,而且最重要的是还清晰地描绘出了时钟Clock从输入到输出的路径配置,帮助用户理清整个系统时钟管理的结构。

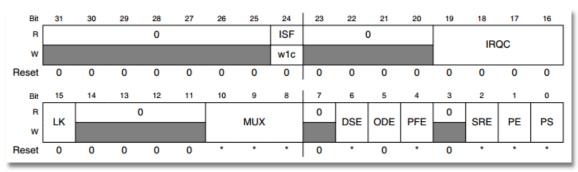

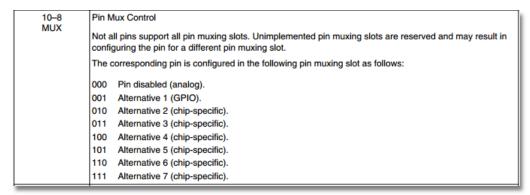

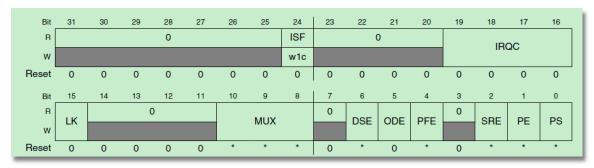

### 4.3.3 管脚复用

ARM平台丰富的外设资源与有限的管脚封装之间的矛盾造成了其管脚复用的必然性(除了个别敏感的管脚外),而不同于时钟管理部分的复杂,飞思卡尔对其芯片管脚复用的配置却非常简单。对芯片管脚复用的配置需要结合Datasheet中"Pinout"章节的管脚分配图如图 86,而所需要配置的寄存器可以在"Port Control and Interrupt"这一章中找到,即PORTx\_PCRn(其中x表示A、B、C、D、E、F等管脚组,而n则表示0~31之间的管脚号),如图 87所示,通过这种PORT分类的方式来映射芯片所有管脚。该寄存器中3位MUX即表示复用功能的选择如图 88,最多8个复用的选项一般足够了。当然,根据所选择的复用外设的需要也可以通过该寄存器使能上拉下拉电阻功能,还有相应的I/O外部中断也需要在此寄存器里做相应配置。

| 121<br>BGA | 100<br>LQFP | 64<br>LQFP | 64<br>Map<br>Bga | Pin Name               | Default       | ALT0          | ALT1                   | ALT2          | ALT3            | ALT4 | ALT5 | ALT6     | ALT7           | EzPort |

|------------|-------------|------------|------------------|------------------------|---------------|---------------|------------------------|---------------|-----------------|------|------|----------|----------------|--------|

| E4         | 1           | 1          | A1               | PTEO/<br>CLKOUT32<br>K | ADC1_<br>SE4a | ADC1_<br>SE4a | PTEO/<br>CLKOUT32<br>K | SPI1_PCS1     | UART1_TX        |      |      | 12C1_SDA | RTC_<br>CLKOUT |        |

| E3         | 2           | 2          | B1               | PTE1/<br>LLWU_P0       | ADC1_<br>SE5a | ADC1_<br>SE5a | PTE1/<br>LLWU_P0       | SPI1_<br>SOUT | UART1_RX        |      |      | I2C1_SCL | SPI1_SIN       |        |

| E2         | 3           | _          | -                | PTE2/<br>LLWU_P1       | ADC1_<br>SE6a | ADC1_<br>SE6a | PTE2/<br>LLWU_P1       | SPI1_SCK      | UART1_<br>CTS_b |      |      |          |                |        |

图 86 Pinout 管脚复用分配图

图 87 PORTx\_PCRn 寄存器映射

图 88 管脚复用配置位

结合上述三图,以配置64 pin LQFP封装的芯片MK22FN512VLH12的PTE0和PTE1这两个管脚为UART 功能为例,它们默认的配置为ADC的模拟输入端口功能,通过图4管脚复用分配图找到UART1的复用索引号为ALT3选项,则只需要将PORTE\_PCR0和PORTE\_PCR1这两个寄存器中MUX位写入3即可实现UART1\_TX和UART1\_RX端口的配置,操作代码如下:

PORTE\_PCR0 |= 3 << 8; PORTE\_PCR1 |= 3 << 8;

#### 4.3.4 中断管理

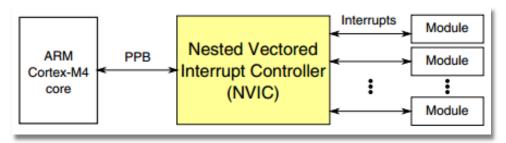

图 89 NVIC 模块框图

ARM平台的中断管理引入了NVIC即嵌套向量中断控制器这个模块,其负责接管芯片运行状态下所有的中断源,是ARM内核不可分离的一部分,它与内核的逻辑紧密耦合完成相应的中断处理工作。而且由于其为内核的一部分,因此关于NVIC相关寄存器的配置需要结合ARM公司的架构技术文档,具体见内核架构参考手册(Architecture Reference Manual。不过,NVIC对中断的管理是建立在中断向量表上的,这张表的数量是固定的,但是除了前16个内核中断之外,剩余的IRQ中断不同的半导体厂家可以根据自己的需要来定制映射不同的外设中断,也就是说各大半导体厂家定义的这个中断向量表可能不一致,飞思卡尔ARM平台的中断向量表映射可以在其Reference Manual的"第三章 Chip Configuration"中Core Modules的Nested Vectored Interrupt Controller (NVIC) Configuration小节中找到,用户可以根据这张表的索引号来使能或者禁用相应的IRQ中断。

# 4.4 用户指南 (User Guide)

为了方便新用户快速入门和熟悉飞思卡尔的产品、开发工具和开发环境,飞思卡尔针对其相关产品提供了相应的用户指导手册,包括部分外设资源模块的编程指导手册和相应的开发板工具使用手册。

# 4.4.1 外设模块快速参考用户指南(Peripheral Quick Reference User Guide)

外设模块用户参考手册详细介绍了芯片常用模块的技术特性,并针对该模块资源的部分功能给出了相应的代码例程作为编程参考,可以加快用户上手时间,提高用户开发的效率,在软件开发时可以结合该用户手册和芯片的Reference Manual文档中相应外设模块的章节进行外设资源的配置。飞思卡尔为ARM平台Kinetis家族的部分系列提供了相应的外设用户参考手册,如表 2所示。

| MCU 系列    | 文档名称及链接       |

|-----------|---------------|

| Kinetis K | KQRUG         |

| Kinetis L | <u>KLQRUG</u> |

| Kinetis V | <u>KVQRUG</u> |

表 2 Kinetis 家族外设模块用户参考手册

#### 4.4.2 评估板用户指南 (Freedom & TWR Tool User Guide)

为方便用户评估芯片的性能和熟悉飞思卡尔产品的开发流程,飞思卡尔提供了两套评估板供用户评估和开发测试,其中Freedom板为廉价的评估板,自带板载调试器,用户可以直接通过自己的PC机快速搭建开发环境并进行测试和评估芯片简单的外设资源,另外塔式系统Tower板为可扩展性比较强的评估板,板载资源比较丰富且通过构建塔式系统可以灵活的添加和裁剪外设资源,用户可以进行更高级的功能测试。飞思卡尔为这两套评估板均提供了相应的用户指导手册帮助用户快速入门飞思卡尔产品的开发,以MK22F系列为例,Freedom板的用户手册为FRDMK22FUG,TWR板的为TWRK22F120MUG,它们均可以直接在飞思卡尔官网搜索下载。

# 4.5 其它的技术文档

除了上述Datasheet、Reference Manual和User Guide之外,飞思卡尔还提供了其他的丰富的技术文档供用户参考,本章节重点介绍一下用户还经常参考的应用笔记、Errata勘误表和内核架构的参考文档。

# 4.5.1 应用笔记(Application Notes)

Application Note,即应用笔记,是飞思卡尔内部专家工程师针对飞思卡尔产品的具体应用所撰写的心得笔记。飞思卡尔官网系统提供了大量的中英文应用笔记供客户工程师参考和学习,一些应用笔记也会附上相应的代码例程工客户下载。飞思卡尔应用笔记均以其英文大写字母"AN"开头,后面数字为文档的序列号,用户可以直接在飞思卡尔官网搜索相应的文档序号或者具体应用的关键字进行下载,此外针对某款芯片相关的应用笔记则可以直接在该芯片的产品页中"Document"一栏中找到,如图 90所示。

图 90 应用笔记列表

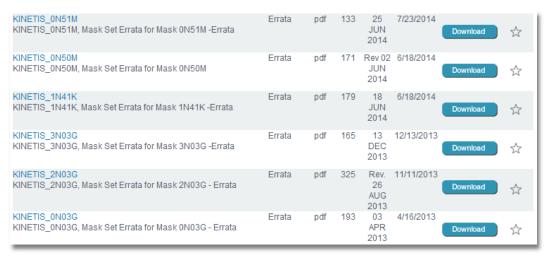

### 4.5.2 勘误表 (Mask Set Errata)

芯片的Errata勘误表是客户在使用相关芯片进行项目开发时必须要查阅的参考文档,在一款芯片从发布到量产再到最后停产的整个生命周期里,半导体厂商会非常负责任地针对芯片在应用过程中出现的一些功能的局限性或者某些参数的不准确性等问题不定时的发布相应的勘误表,帮助用户在项目开发过程中规避相应的问题和进行风险把控。此外,需要用户注意的是,Errata勘误表是以Mask Set即芯片的掩膜硅版本号进行分类的(芯片Package封装上打的标号,比如2N03G),所以用户可以根据所使用芯片的版本号在飞思卡尔官网查询相应的Errata勘误表文件,同样用户也可以直接到相关芯片的产品页中Document一栏中找到该芯片系列所有Mask Set的Errata勘误表,以K22F120M产品为例,其所有子系列的Errata勘误表如图 91所示。

图 91 K22F\_120M 勘误表

### 4.5.3 内核架构参考手册(Architecture Reference Manual)

由于飞思卡尔Kinetis家族系列的平台是基于ARM Cortex-M内核的产品,其内核的知识产权为ARM公司所有,所以关于该平台内核架构部分的包括指令集、中断管理和调试组件等详细的技术信息则需要到ARM公司官网下载相应内核架构的技术文档作为参考,由于飞思卡尔目前的Kinetis产品系列主要为ARM Cortex-M0+和Cortex-M4内核,其在ARM官网相应的内核参考文档可以直接搜索得到,其相应的文档链接如下:

- 1. ARM Cortex-M4 内核技术参考手册

- 2. ARM Cortex-M0+内核技术参考手册

此外,关于飞思卡尔的自有内核架构包括DSP56800E/EX和Coldfire等相关内核架构的文档则可以直接在飞思卡尔官网下载。

1. DSP56800E/DSP56800EX内核技术参考手册

# 5 飞思卡尔单片机硬件设计指南

# 5.1 概述

在进行嵌入式系统设计时,硬件电路设计的好坏不仅关系到整个系统的功能实现和可靠性,还会对系统软件的复杂程度产生影响。本章节以Kinetis K22芯片为对象,介绍采用Kinetis MCU进行最小系统硬件设计时,需要了解的一些硬件设计注意事项和设计原则。

在本章节中,除了会介绍电源电路、时钟电路、复位电路、调试电路等MCU常见外围硬件设计外,还会针对使用Kinetis系列芯片时需要了解的设计做一些探讨,如NMI引脚配置、High current driver引脚分布、IO输出方式(Open-drain/Pull-Push)支持、RTC、USB、ADC电路设计和参考电压的选择以及板级EMC性能改善等。

### 5.2 电源电路的设计

### 5.2.1 K22的电源引脚分配和功能描述

Kinetis K22支持1.71-3.6V宽电压输入,为了提供稳定的电源,芯片使用多组电源引脚分别为内部电压调节器、IO引脚驱动、AD转换电路等供电,并且提供多处电源引出脚,便于用户外接滤波电容,改善系统的电磁兼容性。对于本文档中使用到的K22 LQFP-64 pin封装,其电源引脚名称、分布和功能描述如表 3所示。

| 表 3 K22 L( | )FP-64 nir | 封装电源引脚名称、 | 分布和功能描述 |

|------------|------------|-----------|---------|

|            |            |           |         |

| 引脚名称          |                        | 功能描述               | 典型值     | 引脚号(LQFP-64)    |  |

|---------------|------------------------|--------------------|---------|-----------------|--|

|               | VDDx/VSSx <sup>1</sup> | 数字电源输入正/负          | 3.3V、0V | 3/4、30/31、48/47 |  |

|               | VDDA/VSSA              | AD 模块的电源输入正/负      | 3.3V、0V | 13、16           |  |

| 电源输入          | VREFH/VREFL            | AD 模块参考电压输入高/<br>低 | 3.3V、0V | 14、15           |  |

|               | VBAT                   | RTC 模块的备用电源输入      | 3.3V    | 21              |  |

|               | VREGIN                 | USB 模块输入参考电压       | 5V      | 8               |  |

| 电源输出          | VOUT33                 | USB 模块电源稳压器输出      | 3.3V    | 7               |  |

| 2037 1113 224 | VREF_OUT               | 内部参考电压输出           | 1.2V    | 17              |  |

<sup>1.</sup> 文中VSSx指的是芯片的地

### 5.2.2 MCU主电源供电引脚

VDDx/VSSx是芯片的主电源供电引脚,Kinetis K22 LQFP 64 pin封装的芯片上一共包含3对,在电路设计时需要在每对引脚外部分别放置至少一个去耦电容(0.1uF的陶瓷电容)。并且旁路电容的放置必须尽量靠近 MCU 电源引脚,从而最大限度地缩小 VDD和 VSS 引脚之间的电容所形成的环路。

在芯片内部,这三对电源的引脚是互相连通的。理论上说,只要将任意一个VDDx引脚和任意一个VSSx引脚连接到电源上,整个芯片就可以正常工作了。但在实际的设计中,我们建议将三组电源引脚都可靠地连接到电源上,这样对改善芯片内部的电源回路以及提高整个系统的EMC性能都更有好处。

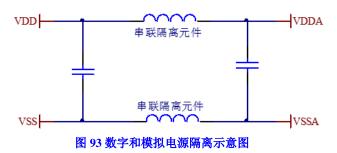

### 5.2.3 模拟外设电源及参考电压引脚

VDDA/VSSA是芯片内部ADC、DAC以及CMP等模拟外设的电源输入引脚,为使芯片的模拟外设有稳定的电源,从而得到更好的转换精度,通常需要在靠近VDDA引脚的地方并联两个外部稳压电容(10nF陶瓷电容+1 μ F钽电容)。另外,为限制电源中的高频噪声,在设计时,可以将VDDA通过电感、磁珠等阻塞元件与数字电源VDDx进行隔离。

另外,大部分Kinetis MCU还提供了一对模拟参考输入引脚VREFH/VREFL,用户可以连接一个独立的外部电压基准作为模拟电压的参考(该基准的电压范围为1.13V~VDDA)。客户也可以使用片内产生的内部ADC参考源,一般为1.2V。为保证能得到更好的精度,建议使用外部的3V电压作为参考。当然,用户也可以直接连接到外部电源引脚VDDA上,使用过程中,建议在VREFH引脚上连接一个10nF和一个1 μ F的电容。对于一些小封装的芯片,可能没有VREFH和VREFL,实际上它们分别在内部被直接连接到ADC的供电电源VDDA和VSSA。

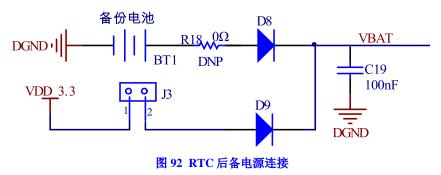

### 5.2.4 RTC后备电源引脚

VBAT引脚是RTC模块的备用电源输入,用于在系统掉电和低功耗模式下为RTC和一个32字节寄存器供电,该引脚通常被连接到外部电池(1.71V < VBAT < 3.6V)。如图92所示,一个简单的电池隔离器由一个共阴极的双肖特基阵列组成,在主系统电源VDD关闭时,通过器件D1提供备用电池。建议在尽可能靠近MCU的地方放置一个100nF旁路电容,以便最大限度地降低电源切换事件的影响。

#### 5.2.5 USB模块电源引脚

VREGIN是芯片内部USB模块的供电引脚,为避免外部瞬态浪涌电压的影响,建议在此引脚的线路上串连一个内阻为330欧姆的磁珠,并在靠近该引脚处并联一个10uF电容,如果成本允许,考虑在此供电线路靠近USB物理接口侧并联一个TVS管,作为热插拔和外部浪涌电压的保护电路。

### 5.2.6 VREF\_OUT和VOUT33电压输出引脚

为方便用户使用,Kinetis K22还有两个电压输出引脚,用户可以通过程序配置分别对外输出一个1.2V电压和一个3.3V电压。其中,VREF\_OUT引脚是芯片内部1.2V基准电压的输出引脚,该电压可以作为芯片内部ADC,DAC或者CMP作为电压基准,同时也可以作为外部电路的电压源。需要注意的一点是,无论是在内部或者外部使用该1.2V电压作为参考,都需要在VREF\_OUT引脚连接一个100nF的负载电容。

VOUT33引脚是芯片内部3.3V电压的输出引脚,该电压是由芯片内部USB Voltage Regulator产生,该电压除了可以用来提供给内部的USB Transceiver完成USB功能外,用户还可通过VOUT3.3引脚输出到外部,提供给板上的其它芯片作为供电电源,其最大输出电流为120mA。并且通常建议在靠近该引脚外部加一个2.2uF电容。

#### 5.2.7 电源电路的PCB设计建议

电源系统的布线是整个硬件版图最重要的部分,其基本思想是确保 MCU 和其他数字器件通过低阻抗路径接至电源,并且有一些常规可以遵循:

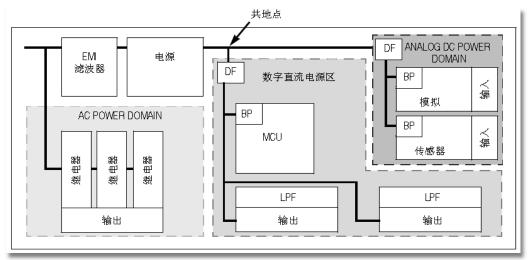

1. 分割不同的电源域,将交流电源与直流电源分开,数字部分与模拟部分分开。实际电路设计中可以选择使用物理隔离和去耦滤波器,对于后者的使用如图 93所示,串联隔离元件通常选择小电感或阻抗较小(100 MHz时约 100 Ω)的铁氧体磁珠。去耦电容一般选择10nF 到 1uF,具有高频成分的一端应选择较低的值。

- 2. 在MCU的每个VDD电源引脚旁边放置去耦电容,画板时一定要尽量使去耦电容靠近MCU电源引脚放置,并尽量缩小VDD和VSS引脚之间的电容所形成的环路。

- 3. 合理使用电源层和接地层,接地布线应优先于任何其他布线,电源走线尽量使用较宽走线和较少的层变换。在系统允许的情况下,建议在 MCU 封装的正下方使用一个接地层,以便降低 RF 辐射并提高瞬变抑制性能,提高板级的EMC性能(更多关于电源硬件设计和EMC的知识请参看AN2764)。

### 5.3 时钟电路

### 5.3.1 K22的时钟源

为满足用户不同的应用,飞思卡尔Kinetis MCU提供多个时钟源选择,图 94所示是K22的系统时钟框图,它包括多种时钟源,可以通过MCG模块灵活地配置使用。其中内部时钟源的优点是成本低,不易受外部影响,而外部时钟源的优点在于能产生非常精确的主时钟。

- 1. 内部时钟源:

- 在芯片内部集成了一个4M Hz快速时钟和一个32K 慢速时钟;

- 一个1K Hz固定输出的LPO,可以工作在任何的低功耗模式下;

- 内部IRC48M, 主要用于USB等对时钟精度要求比较高的应用。

- 2. 外部时钟源:

- 在EXTAL0和XTAL0之间可以外接振荡器或者在EXTAL0引脚直接连接时钟源,频率范围 为从 32.768Khz到32Mhz;

- 在EXTAL32和XTAL32之间可以外接32768Hz无源振荡器或者有源时钟作为RTC或者MCU 系统的时钟源。

图 94 K22 的系统时钟框图

#### 5.3.2 MCG的外部时钟振荡器电路设计

常用的外部时钟振荡器有两种类型:机械谐振式,如石英晶体和陶瓷谐振器;被动式RC(电阻-电容)振荡器。关于该振荡器的元件选用详见特定器件的Datasheet手册,此处不再赘述。本节主要针对使用外部晶体振荡器的时钟电路设计展开探讨。

#### 5.3.2.1 外接晶振的电路设计

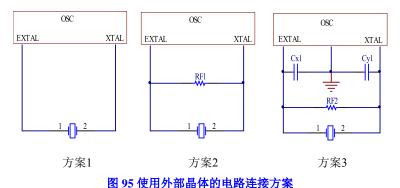

根据应用的不同,Kinetis连接外部晶振时可以采用3种电路设计,如表4所示。

| 晶振和应用类型                             | 建议电路      |

|-------------------------------------|-----------|

| Low-frequency(32 kHz), Low Power    | 方案 1      |

| Low-frequency(32 kHz), High Gain    | 方案 2/方案 3 |

| High-frequency(3-32 MHz), Low Power | 方案 1/方案 3 |

| High-frequency(3-32 MHz), High Gain | 方案 2/方案 3 |

表 4 Kinetis 使用不同外部晶体外部电路方案选择

具体的电路连接分别如图 95所示,可以看到,在方案1和方案2中不需要外部谐振电容,原因是在芯片的内部集成了谐振电容,用户可以通过CR[SCxP]位来灵活配置内部谐振电容的大小,其最大值可以达到30 pF。而当选用的晶振所需要的匹配电容大于30pF时,建议采用方案3的晶振连接,否则建议使用方案1和方案2,从而简化电路设计。

需要指出的是,尽管方案3可以在多种模式下使用,但是在低功耗模式使用时,由于芯片振荡器内部默认是集成反馈电阻的,所以一定不要外部再加 $R_F$ 。对于 $C_X$ 和 $C_y$ ,负载电容的容值需要根据晶振的要求进行选择。

对于RTC外部32K晶振输入,由于芯片内部包含反馈电阻和谐振电容,只需似方案1在EXTAL32和XTAL32引脚外接32K晶振即可,无需外接电容和电阻,从而可大大简化电路设计。

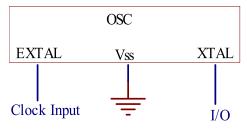

#### 5.3.2.2 外接有源振荡器的电路设计

如果采用外部有源时钟,其电路设计就会更加的简单,如图 96所示。对于K22, 其外部有源时钟的最大值为50MHz。

图 96 使用外部有源振荡器的时钟电路设计

#### 5.3.2.3 晶振电路PCB设计建议

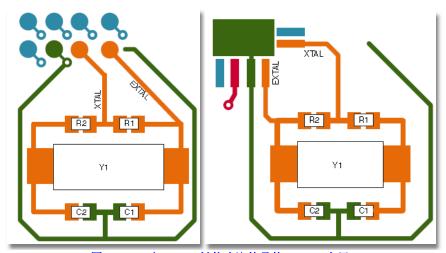

Kinetis MCU的引脚布局考虑到PCB布板的需要,通常将EXTAL 和 XTAL 引脚置于 BGA 封装的外部焊盘环上或QFP封装的拐角上,从而为在顶层上靠近 MCU 处放置晶体或谐振器的布线提供空间。通常在时钟引脚的旁边还会有地(VSS)引脚,方便用户的接地布线。以下是一些通用的规则:

- 1. 晶体和负载电容需要尽可能近地靠近MCU的引脚,以减小输出失真和启动稳定时间;

- 2. 晶体正下方的层上不得有任何种类的信号布线:

- 3. 合理选用偏置电阻和负载电容,涉及到EMC易感性的系统中,应该选用可以使振荡器输入引脚上信号的振幅比较大的那种振荡器配置,但带来后果可能是功耗会比较大;

- 4. 晶体及其负载元件周围应放置一个防护环,防止安装层上的相邻信号发生串扰。此防护环可以从晶体引脚相邻的 VSS 引脚起始,图 97所示分别是推荐的BGA封装和LQFP封装的晶体Layout布局。

图 97 BGA 和 LQFP 封装建议的晶体 Layout 布局

# 5.4 复位电路设计

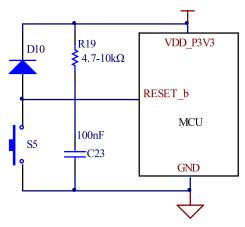

在基于MCU的系统中,除振荡器输入之外的最敏感的输入信号就是复位和中断请求输入。 RESET\_b引脚是芯片的复位引脚,该引脚默认是使能复位功能的(可通过软件配置为GPIO等其它 功能),并且低电平有效。Kinetis MCU的复位引脚是双向引脚,作为输入端,将其拉低可以使芯片复位;作为输出引脚,上电复位期间会有低脉冲输出,表示芯片复位完成。

建议的电路如图 98所示,通过上拉电阻把该引脚拉至高电平,同时靠近 MCU 放置一个100 nF电容,以实现瞬态保护避免误复位。值得一提的是,RESET\_b 引脚还有一个可配置数字滤波器,用以在上电之后抑制该引脚上的潜在噪声(相应配置位位于RCM\_RPFC寄存器)。如果使用该滤波器的话,上述的上拉电阻和电容可能变得不需要,但在高电气噪声环境中,仍然建议使用外部滤波。

图 98 典型复位电路设计

### 5.5 调试接口

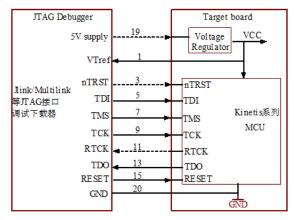

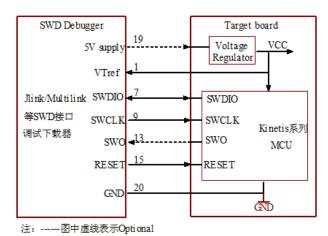

Kinetis MCU同时支持JTAG接口和SWD接口进行编程调试。除电源外,JTAG接口需要用到至少5个PIN脚(JTAG\_TCLK/ JTAG\_TDI/ JTAG\_TDO/ JTAG\_TMS/ JTAG\_RST),其电路连接如图 99 所示,而串行线调试接口(SWD)最少只需要3个Pin 脚(SWD\_CLK/SWD\_DIO/SWD\_RST),其电路连接如图 100所示。两者相比,SWD在高速模式下更稳定,使用引脚更少,所以在使用过程中建议使用SWD接口。

注: -----图中虚线表示Optional

图 99 Kinetis MCU JTAG 接口连接示意图

图 100 Kinetis MCU SWD 接口连接示意图

## 5.6 ADC模拟输入

模拟采样是MCU的一个常用功能,Kinetis 大部分MCU系列提供16位的SAR ADC,最多支持4个独立ADC模块以及48个通道(单端,在不考虑引脚复用的情况下),本文档中使用的MK22FN512VLH12包含两个独立ADC模块,支持14个单端通道和2个差分通道。

对模拟输入而言,前端滤波电路的设计非常重要,除了考虑模拟信号的截止频率,还需要考虑源阻抗和采样时间,尤其是对于高分辨率模数转换。常规思想是: 快速采样时间与慢速采样时间相比,要求更小的电容值和输入阻抗。高分辨率输入与低分辨率输入相比,要求的电容值和输入阻抗可能更小。一般而言,并联电容值范围是  $10\,\mathrm{pF}$  (高速转换) 至  $1\mu\mathrm{F}$  (低速转换),串联电阻的范围是数百欧姆到  $10\,\mathrm{k}\,\Omega$ 。除了合理设计外部滤波电路,模拟电路在PCB布线时还有很多需要注意的地方:

- 1. AD通道的布线要尽量短;

- 将数字部分和模拟部分的电源分开,并分区覆铜,保证模拟地和数字地只在一个点结合, 而且这个点要求远离干扰,有时会选用一个磁珠连接;

- 3. 走线周围避免放置高噪声元器件,在模拟通道外围使用模拟地进行隔离;

- 4. 要想得到特别准确的采样结果,一般推荐在输入端加一些Buffer/跟随运放。

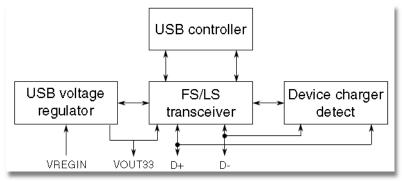

## 5.7 USB电路设计

Kinetis K22内部USB模块的系统框图如图 101所示,它集成了一个支持Dual-role USB OTG-capable (On-The-Go) 的控制器模块、一个Transceiver、一个3.3 V regulator以及一个USB device charger 检测模块,支持USB 2.0规格的FS(full-speed)Device 模式和 FS/LS host模式。

图 101 K22 内部 USB 模块系统框图

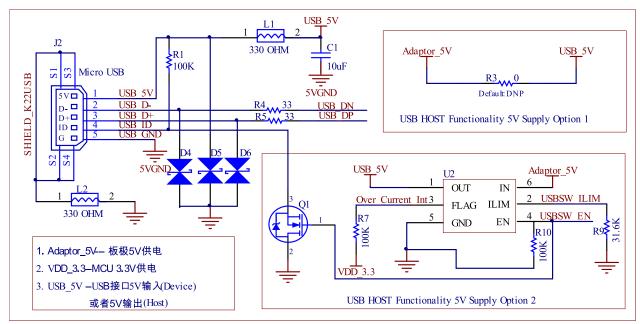

Kinetis USB模块的完善大大简化了USB的接口电路设计,但是用户还是需要根据使用模式的不同进行一些外部电路的设计。图 102是USB在Device和Host模式下的推荐电路,其中Option 1和Option 2是MCU工作在Host模式下,实现对外部USB Device提供5V电压的电路图。Option 1结构简单,成本低,Option 2方便程序控制MCU在Host和Device模式进行切换,可靠性更高。而当MCU只工作在Device模式下,这两个Option可以省略。

图 102 USB Device and Host 模式下电路设计

# 5.8 板级EMC性能改善与PCB布线的注意事项

EMC性能是作为产品认证的一个重要指标,和板级硬件电路的设计息息相关,EMC性能取决于许多因素,通常需要考虑的因素包括:连接器、机械组件、高速信号、低速信号、开关和电源域等。

连接器和某些机械组件(开关、继电器等)的放置对最终产品的成型至关重要,所以在开始PCB布线之前,必须注意妥善安放各元件并合理划分不同的电源域,如图 103所示。必须将低电平模拟信号电路、高速数字信号电路以及噪声电路(继电器、大电流开关等)分开放置,以将PCB子

系统间的耦合将到最低。另外,在每个功能区域内分别添加退耦滤波器(DF)、高频率旁路电容(BP)以及提供低通滤波器(LPF),从而增强系统的整体EMC性能。

图 103 板级平面结构布局

用户可在飞思卡尔网站上搜索应用笔记"AN2321:电路板级的电磁兼容设计"作为参考。

### 5.9 Kinetis MCU的封装类型和一些特殊引脚说明

# 5.9.1 封装类型

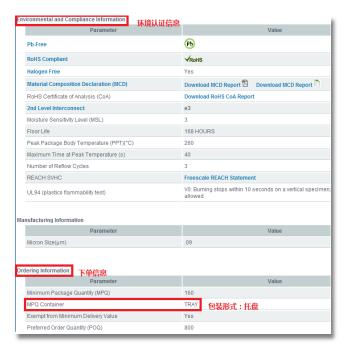

Kinetis MCU提供多种不同的封装类型,从20脚1.6x2.0 mm的CSP封装的KL03到256脚BGA封装的K70,最大程度上满足客户在不同应用场合的需求。关于芯片的封装尺寸信息可以在官网查询,此处以K22F120M 64-pin封装为例讲述一下封装尺寸信息的查找方法,步骤如下面的四个截图所示,在该网页中除了可以找到该芯片的封装信息,还可以找到该芯片的环境合规信息、订购信息、工作特性、供货状态等。

图 104 封装尺寸信息查找方法截图

# 5.9.2 NMI引脚

NMI引脚是芯片的不可屏蔽中断引脚,芯片默认是使能NMI功能的(低电平有效),该引脚内部具有较小的内部上拉电阻,但建议采用外部  $4.7\,k\,\Omega$  至 $10\,k\,\Omega$  上拉电阻。需要特别提出的是,如果该引脚被外部电路拉低,即便该引脚被复用成其它功能(FTM或者GPIO),在下载程序时,也有可能导致芯片与仿真器连接异常。原因是芯片一上电,在程序还没有执行禁用NMI功能时,由于NMI引脚被外部拉低,程序就会已经进入NMI的中断程序,从而造成程序无法成功下载。此时则需要通过Flash NVM 配置字节禁用NMI功能,它与在程序中禁用 NMI引脚的区别在于,这种方法会执行用户程序之前生效。

## 5.9.3 大电流驱动 (High Current Driver) 引脚

Kinetis E系列MCU部分引脚支持大电流驱动功能,可以直接驱动LED,每个引脚的最大输出电流能够达到20mA,总的最大输出电流是100mA。

#### 5.9.4 LLWU唤醒引脚

在Kinetis MCU低功耗应用中,除了支持芯片内部模块唤醒之外,还支持GPIO引脚唤醒,但需要指出的是并不是所有的引脚都支持,所以在电路设计时需要特别注意,具体是哪些引脚支持 LLWU引脚唤醒功能,可以参照芯片RM手册的Chip Configuration章节。

#### 5.9.5 未用到的I/O及模块的处理

在实际应用中,通常会有一些未用到的微控制器资源,如某些特定的内部模块、晶振引脚、以及GPIO引脚等,为了提高EMC性能,需要对这些资源做相应配置。

- 未使用的I/O端口通常设置为一个特定的状态,考虑到提高EMC性能和低功耗应用,通常设置为输出并外部上拉;

- 未使用的晶振引脚建议配置为GPIO功能,避免外部信号的干扰;

- 没有用到的模块应该禁用或者"冻结"。

### 5.10设计最小系统硬件电路的Check List

用户设计K22的最小系统时,可参看表 5进行注意事项的检查。

#### 表 5 最小系统设计 Check list

|   | 引脚/信号           | 注意事项                                                                                                                             |

|---|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| 1 | Reset           | 建议通过电阻把该引脚拉至高电平(4.7k-10k),同时靠近 MCU 放置 100 nF 电容;                                                                                 |

| 2 | NMI             | 引脚内部具有较小的内部上拉电阻,但建议采用外部 4.7 kΩ 至 10 kΩ 上拉电阻,并且 NMI 引脚可以用作低功耗的唤醒引脚;                                                               |

|   |                 | 如果复用为其它功能,且外部拉低,需要通过 Flash NVM 配置 Disable NMI 功能;                                                                                |

| 3 | VTAL/EVTAL      | 根据应用场合的不同选择合适的电路,参见"外接晶振的电路设计"章节;                                                                                                |

| 3 | XTAL/EXTAL      | 不使用时建议配置为 GPIO 输出功能;                                                                                                             |

| 4 | XTAL32/EXTAL32  | 外部不需要匹配电容和反馈电阻;                                                                                                                  |

| 5 | VDDx/VSSx       | 推荐每对电源引脚分别放置至少一个去耦电容(0.1uF 的陶瓷电容)。并且旁路电容的放置 必须尽量靠近 MCU 电源引脚;                                                                     |

| 6 | LLWU Pin        | 并不是所有的引脚都支持 LLWU 唤醒功能,具体可查看芯片 "Chip configuration"章节;                                                                            |

| 7 | SWD_CLK/SWD_DIO | 尽量缩短线的长度 <= 6 英寸,最大程度避免串扰;使用的仿真连接的 USB 线也不要过长,尽量选用质量好一些的短的 USB 线;                                                                |

| 8 | LPUART_TX       | 在 UART transmitter disable 并且芯片进入低功耗状态时,该引脚会出现 tri-state 从而产生漏电流,所以在低功耗应用中建议使能内部上拉功能,或者外部上拉,详细信息参见 <u>Errata:</u> <u>e7986</u> 。 |

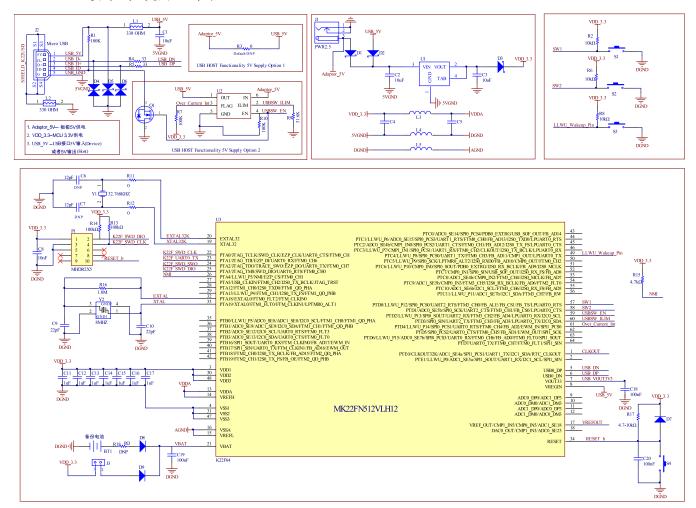

# 5.11K22最小系统原理图

图 105 K22F 120M LQFP-64pin 最小系统原理图

# 6 飞思卡尔单片机软件开发指南

# 6.1 概述

前面的章节介绍了飞思卡尔单片机的硬件设计方法,本章将会详细介绍软件开发的各个环节,让 开发者能够从零开始,快速完成软件开发流程。

# 6.2 开发环境设置与开发工具使用

飞思卡尔的MCU,具备完善的生态系统,支持各种IDE和调试工具,并且提供了各式各样便捷的工具,即使是初学者,也能轻松完成。

### 6.2.1 连接开发板

飞思卡尔提供了种类繁多而且容易使用的开发工具及环境,极易上手,用户可以不用花太多精力 在软件开发之外的东西,只要简单的连几根线,即可开始开发工作。

首先要使用的是飞思卡尔的开发板。能见到的主要有两种,一种是功能强大的Tower塔式系统,一种是功能比较简单的Freedom板。

#### • Tower塔式系统

Tower塔式系统的主板能够单独使用,也可以加入到塔式系统中与其他的板子共同使用。 Tower系统主板带有JTAG或者OpenSDA调试接口,不再需要外部仿真器,只需要一根USB 线连接开发板和电脑即可实现调试下载功能,如图 106及图 106所示。

TOWER

图 106 单独使用塔式系统主板

图 107 完整的塔式系统

### • Freedom 板

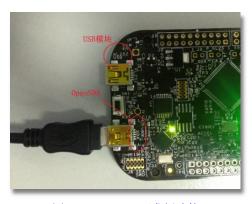

Freedom板与Tower板相比尺寸要小很多,使用方法也更简单。Freedom板带有OpenSDA调试接口,同样不需要外接仿真器,使用USB电缆连接电脑即可。需要注意的是板子上可能会有两个USB插口,一个用于OpenSDA,另一个是芯片本身的USB模块接口,在插口附近会印刷有标识,如图 108所示。

图 108 Freedom 开发板连接

# 6.2.2 使用Kinetis Design Studio(KDS)进行软件开发

选择好开发板之后,就可以开始软件的编写和调试了。飞思卡尔单片机支持所有业内主流的集成开发环境,如IAR、Keil 和CodeWarrior等。开发环境的选择主要是根据用户自己的习惯,本文以飞思卡尔最新的KDS为例来进行说明。

Kinetis Design Studio, 简称KDS, 是飞思卡尔最新推出的针对Kinetis系列MCU的集成开发环境,可以完成整个软件开发过程中的所有功能,包括编辑、编译、调试下载等,目前最新版本1.1.1,可通过此链接下载安装软件和文档:

http://www.freescale.com/zh-Hans/webapp/sps/site/prod\_summary.jsp?code=KDS\_IDE&tid=vanKDS&uc=true&lang\_cd=zh-Hans

KDS基于Eclipse框架,采用ARM GCC和GDB编译调试环境,同时集成了飞思卡尔的Processor Expert和KSDK功能,因为与Codewarrior一样都是基于Eclipse框架,所以使用界面与CodeWarrior几乎一样。KDS专门针对飞思卡尔的Kinetis MCU进行了优化,用户体验更好。

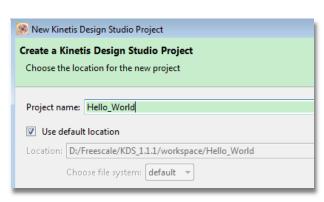

打开KDS后,首先需要选择一个workspace,这里推荐在KDS的安装目录下新建一个专门的文件夹,命名为"workspace"。打开KDS后,我们首先新建一个工程,点击"File"→"New"→"Kinetis Design Studio Project",如图 109至图 110所示。

图 109 在 KDS 中新建工程

图 110 输入工程名称

图 111 选择对应的芯片

最后一步, 选择是否需要辅助开发工具, 如图 112所示。

图 112 选择辅助开发工具

SDK是飞思卡尔提供的软件开发包,里面提供了各个模块常用的API(比如使用UART发送数据),方便用户开发,在本文第三章中有介绍,具体使用方法在后面的章节中有详细的讲解。如果目标芯片支持SDK(比如K22),那么这里可以勾选该选项。

PE(Processor Expert)是飞思卡尔推出的一款图像化配置工具,后面也会详细说明。关于Project Mode选项,如果选择Linked,那么所有的工程都会公用一套静态文件;选择Standalone则会单独 在各自的工程目录下拷贝一份。

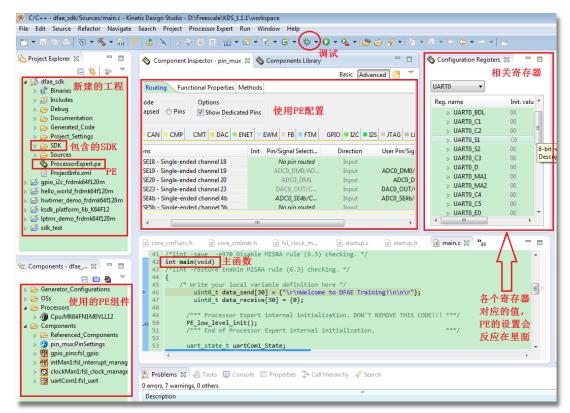

最后一步,点击"Finish"即可完成新工程的创建,KDS开发环境软件的主界面如图 113所示。

图 113 KDS 的主界面

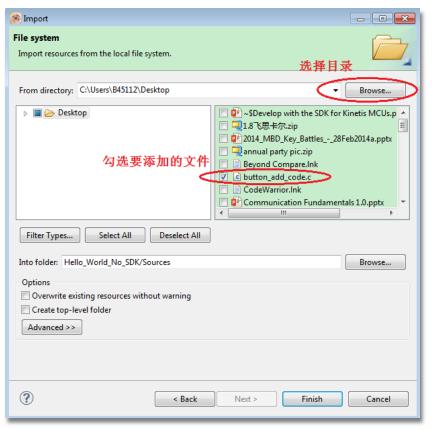

新工程建立完成后,如果用户已经有自己的代码,也可以把他们添加到刚才新建的工程中,如图 114所示。

图 114 添加已有的文件

推荐将用户代码放在"source"目录下面,或者自己新建一个目录,点"next"之后,会弹出一个对话框,如图 115所示。

图 115 添加已有的用户文件

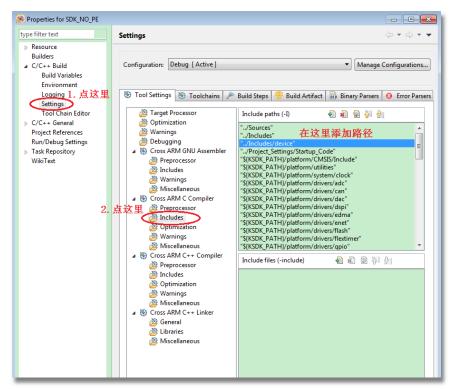

点击"完成"之后,之前选中的所有文件就添加到了工程中。用户也可以通过设置包含路径调用用户文件。在当前的工程上按右键,选"Properties",在弹出的对话框中按图 116操作。

图 116 包含已有的文件

关于PE和SDK的使用,以及MCU具体模块的编程,后面章节会详细讲述,本小节只说明KDS的使用,仅仅在main函数中添加最简单的一行赋值代码为例。

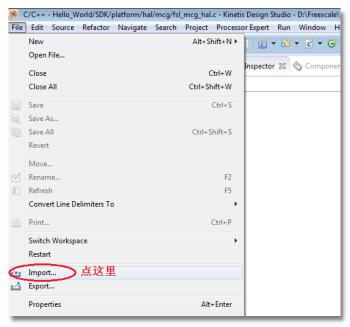

用户除了自己编写程序外,还可以导入现有的工程,这个过程也非常简单,步骤如图 117至图 119 所示。

图 117 导入现有的工程步骤 1

图 118 导入现有的工程步骤 2

图 119 导入现有的工程步骤 3

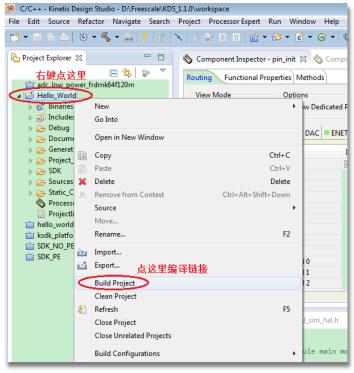

当工程文件都编辑好之后,便可以开始编译调试了。在对应工程上点击鼠标右键,选"Build Project",如图 120所示。

图 120 编译工程

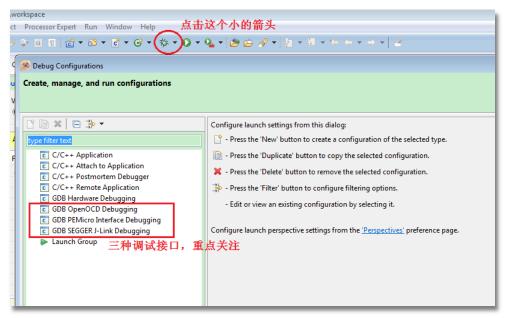

如果代码文件格式没有问题,编译链接通过后,就可以开始调试了。调试开始前,首先需要设置一下使用的调试器。点击小甲虫图标旁边的下拉箭头,再点击"debug configuration",弹出如下对话框,如图 121所示。

图 121 调试接口选择

## 这里我们主要关注三个内容:

1. 选择调试接口。

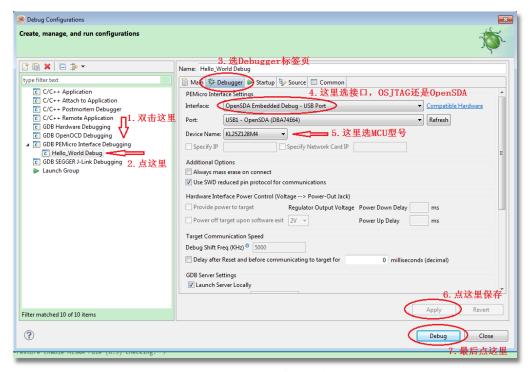

图 121中显示的这三种调试接口,对应于三种不同类型的调试工具,飞思卡尔的Tower板和Freedom板,使用的都是PEMicro的调试接口,这里以PEMicro调试为例进行配置,剩余的两个调试接口的配置类似。双击调试接口的图标,就会出现具体的配置选项,点击"设置",再点击"Debugger"标签,就会出现具体的设置窗口,具体如图 122所示。

图 122 配置调试接口信息

2. 最后点击"Debug"以后,就会开始程序的下载和调试。程序下载完成后会弹出调试界面, 其中各窗口的主要功能如图 123和图 124所示。

图 123 调试界面中的工具栏和寄存器查看窗口

图 124 调试界面中的代码显示窗口

3. 在调试界面上方的工具栏和窗口中,可以单步执行代码,查看寄存器信息;在调试界面下方,可以设置断点,查看当前代码的执行情况等。

KDS还有很多其他的功能和使用方法,用户自己可以在使用中体验,也可以参阅相关文档。

# 6.2.3 处理器专家(PE)的使用

PE(Processor Expert),是飞思卡尔推出的一款图形化设置工具,通过图形化的简洁方式,可以很方便地对MCU的各个模块、功能进行配置,同时自动产生对应的代码。

有了PE的帮助,用户可以避免阅读大篇幅的手册,不需要研究每个寄存器位的含义,只要按照提示进行选择,便可完成对MCU的配置。

PE有两种不同的形式,一种就是前面章节提到的,集成在KDS或Codewarrior里面,直接添加在工程中,可以很方便地调用;另一种是独立的PE软件,全称叫Processor Expert Driver Suite,目前最新版本10.4,可通过如下链接下载:

http://www.freescale.com/webapp/sps/site/prod\_summary.jsp?code=PE\_DRIVER\_SUITE

两种方式的使用方法是一致的,考虑到文档前后的一致性,本文以集成在KDS中的PE的为例,在新建工程的时候勾选PE,便可在工程中通过PE来配置当前的MCU了。下面举例说明PE的最基本的用法。具体的细节后面会有详细的介绍。

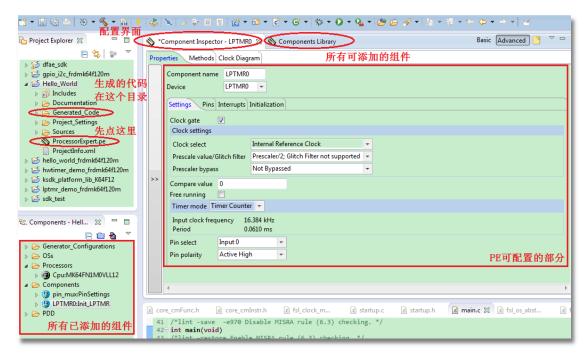

1. 首先,整个PE的配置主界面如图 125所示。

图 125 PE 的配置主界面

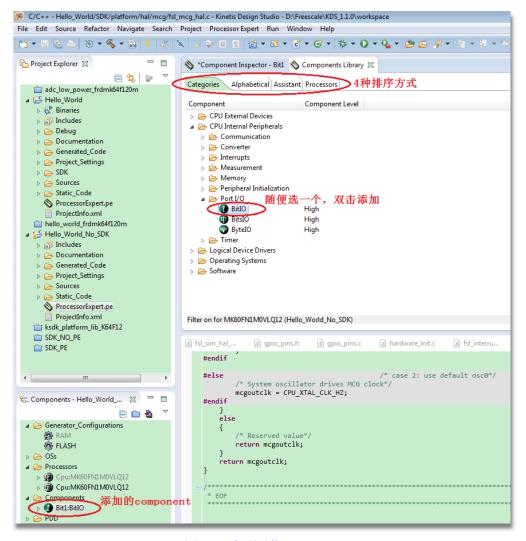

2. 在PE中,MCU的某个外设模块或功能模块称为一个Component(部件)。当用户需要使用哪个模块或功能时,在上图的"Component Library"窗口中添加即可,步骤如图 126所示。

图 126 添加所需的 component

图中标出了"Components"的4种不同的排序和归类方式,用户可以根据自己的习惯使用。 其中"Categories"表示按模块功能分类,"Alphabetical"表示按首字母排序,推荐使用这两种。

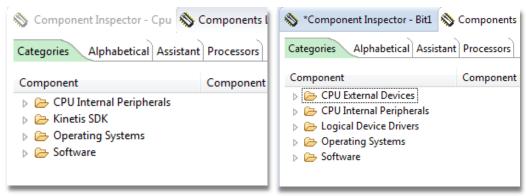

还有一点需要注意,如果添加了SDK,那么PE中的"component"是不一样的,因为SDK 使用的是不同的模块驱动,如图 127和图 127所示。

图 127 有 SDK 时的 Components

图 128 没有 SDK 时的 Components

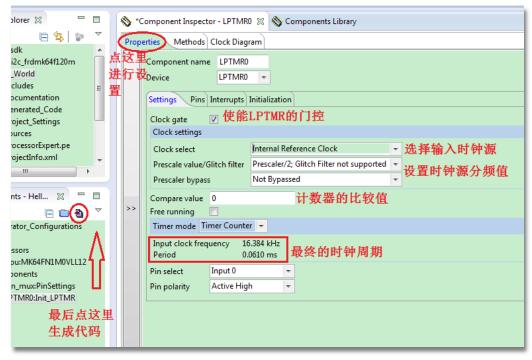

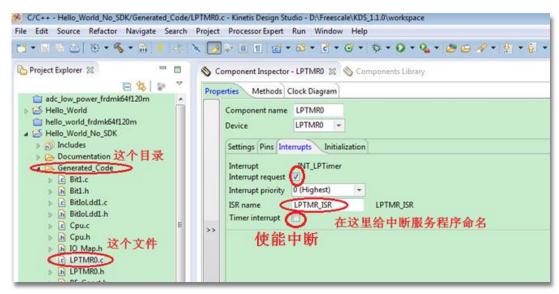

3. 点击所添加的 "component", 就可以对其进行配置了。本文以LPTMR为例来说明如何对 "Component"进行配置。

LPTMR(Low Power Timer)是一个低功耗定时器,在MCU处于低功耗模式下时,仍然能够通过给定的输入时钟源,正常计数并产生中断。LPTMR内部包含一个自动递增的计数器,并能与给定的值进行比较,产生中断等动作。在PE中对LPTMR进行配置的步骤如图 129 所示。

图 129 在 PE 中对 LPTMR 进行配置

按照上图的步骤,就可以完成对LPTMR的配置了。图 129中那些选择项的内容就是对 LPTMR进行配置的细节,LPTMR控制寄存器的每个bit位的定义都会体现这里,用户不用 再去阅读手册具体的细节,只要根据这个图形化界面的说明进行选择即可。生成代码前,请点击保持按钮保存之前的修改。

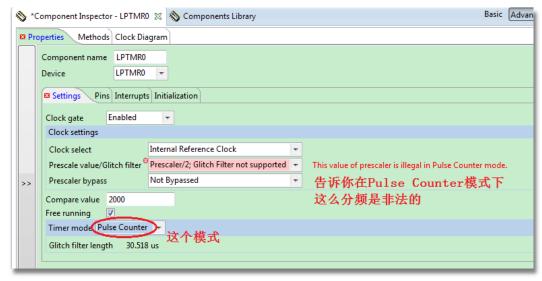

这里有两点需要说明:

一 首先,图形化的配置界面虽然简单,但是并不是可以随心所欲的配置,模块本身有自己的一套工作流程,不同的bit位之间可能会存在关联,因此有可能出现配置冲突。如果用户是手动输入的代码,则很难发现对这种bit位赋值错误;如果是用PE进行配置,就会自动提示报错,如图 130所示。

图 130 PE 的出错提示

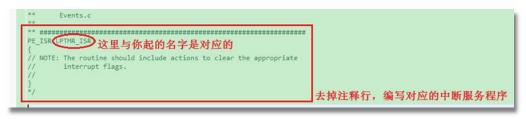

— 另外,如果需要开启LPTMR中断,则需对其中断进行配置,如图 131所示,另外还需要编写相应的中断服务程序。在Generated\_Code目录下,可以找到与配置模块对应的c文件,本例使用的模块是LPTMR0,所以对应的文件是LPTMR0.c,里面可以看到PE生成的中断服务程序原型,如图 132所示。

图 131 在 PE 中开启并设置中断

用户可以在LPTMR0.c文件中,加入自己的中断服务程序代码。

图 132 编写中断服务程序

因为功能不同,不同"component"的配置差别较大,这里就不一一介绍了,但使用起来都是非常简单直观的,用户在可以在使用的时候自己体会。

## 6.3 基本外设模块编程举例

通过前面的步骤,我们对飞思卡尔Kinetis MCU的开发环境、开发工具都有了初步的认识,也熟悉了基本的用法,可以正式开始编写自己的应用代码了。每一个MCU都会包括大量的外设模块,但是不同系列MCU的相同模块一般具有相同的IP,因此软件的开发也大同小异,可以很方便的从一个系列,如K60,移植到另一个系列上,如K20。本节会选出几个最具有代表性的模块,并结合参考代码,介绍其编程方法。

在开始本节之前,首先需要介绍一下赋值语句的使用。MCU的编程,很大程度上就是对寄存器的赋值操作。在飞思卡尔的手册中,每一个寄存器都会有一个名字,同时每个寄存器里的每个bit位也会有一个名字,比如SIM\_SCGC5寄存器,其中有一个PORTA位。同时我们对每个bit位也会定义一个mask,比如SIM\_SCGC5\_PORTA\_MASK,这个mask表示对这个寄存器的PORTA位的掩膜位。所以如果要对这个PORTA位置1,可以用这样的代码:

SIM SCGC5 |= SIM SCGC5 PORTA MASK;

同样如果对这一位清0,代码可以这样:

SIM SCGC5 &= ~SIM SCGC5 PORTA MASK;

这种位操作语句可以方便地对每一个bit进行赋值操作。

# 6.3.1 时钟模块

时钟设置是嵌入式系统的核心,这一节将会详细介绍Kinetis MCU的时钟系统,说明怎样具体配置各个模块的时钟。以Kinetis K22为例,其时钟系统框图如图 133所示。

图 133 Kinetis K22 的时钟系统框图

从图 133中可以看到,K22包括了MCG模块、SIM模块、振荡器模块以及电源管理模块PMC。其中振荡器模块主要是提供各种频率的时钟源;电源管理模块提供一个1KHz的低功耗时钟;而完成整个系统的时钟配置,最关键的是MCG和SIM这两个模块,下面分别进行介绍。

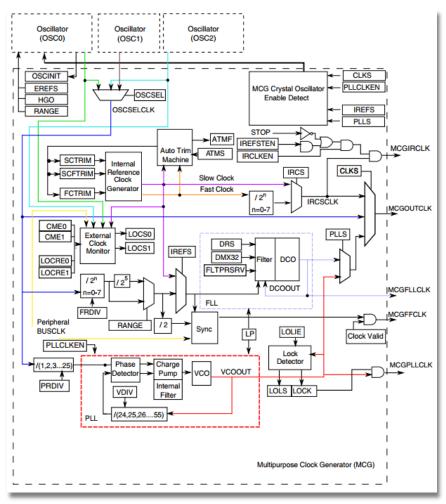

## 6.3.1.1 多用途时钟发生器 (MCG)

MCG(Multipurpose Clock Generator)模块内部包含锁相环(PLL)和锁频环(FLL),还有两个片内时钟:片内高速时钟(4MHz)和片内低速时钟(32KHz)。用户可以根据需求选择不同的时钟源,配置不同的时钟分频因子,来产生各种不同频率的时钟信号。

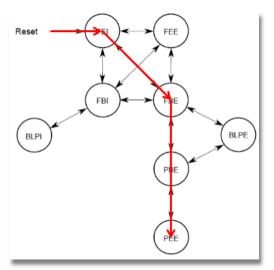

根据PLL/FLL的使用情况,以及内外时钟的选择,MCG提供了9种不同的工作模式,分别是:

- 锁频环工作片内时钟模式 (FEI)

- 锁频环工作片外时钟模式 (FEE)

- 锁频环旁路片内时钟模式 (FBI)

- 锁频环旁路片外时钟模式(FBE)

- 锁相环工作片外时钟模式(PEE)

- 锁相环旁路片外时钟模式(PBE)

- 低功耗旁路片内时钟模式(BLPI)

- 低功耗旁路片外时钟模式(BLPE)

- 停止模式(STOP)

锁频环工作片内时钟模式(FEI)是MCG模块默认使用模式。MCG模块的不同工作模式(停止模式除外)之间可以来回自由切换,如图 134所示。图 134中标示的不是标准的模式转换图,只是其中一种方式而已。这里,以客户最常用的PEE模式工作为例,描述了芯片从上电到最终进入PEE模式的转换过程。

图 134 MCG工作模式转换图

其中MCU上电后的默认模式是FEI,在启动代码中,会经过图中红线标示的状态,最终进入PEE模式。与此对应的时钟分配如图 135所示。

图 135 PEE 模式下的时钟分配

MCG的编程,核心就是对各个分频因子的配置,以及PLL/FLL模块的设置。对MCG模块编程,当然可以采用读手册,写寄存器的方式来进行,但是MCG模块功能相对较复杂,寄存器很多,手册阅读也较吃力,这么开发软件的话,效率不高,这里推荐采用PE工具(Processor Expert)来生成对应的软件代码,本文与前面的一样,也采用KDS环境。

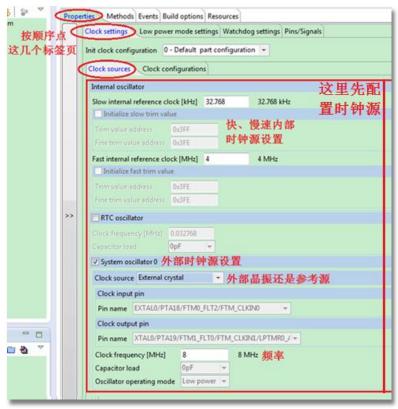

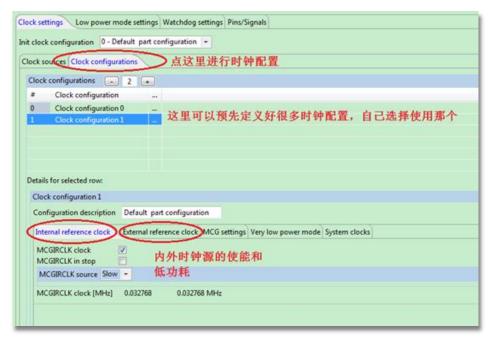

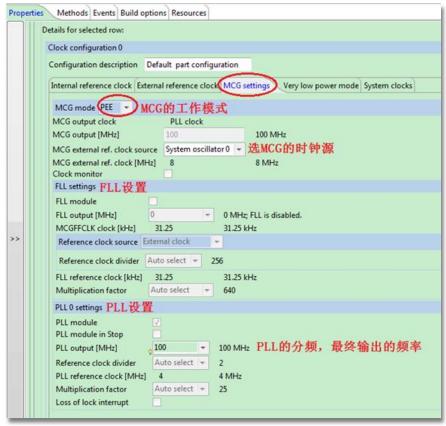

打开KDS后,在左侧点"Processor Expert",就会出现时钟设置页面。因为对于MCU来说,时钟的设置是必需的,所以不需要像另外的模块一样来添加"Component"。配置时钟可按图 136到图 139所示的步骤进行。

图 136 设置系统的时钟

图 137 对时钟源进行配置

图 138 MCG 的设置

图 139 MCU 时钟设置设置

按照上面的步骤,便可以完成整个系统的时钟设置。前面的步骤中,有一些选项是灰色不可操作状态,这和当前MCG模式有关,本例中选择的是PEE模式,因此不能对FLL模块进行设置,此时有关FLL的设置选项就是灰色的。

## 6.3.1.2 系统集成模块(SIM)

SIM(System Integration Module)模块控制芯片内核时钟、总线时钟、外部总线时钟、FLASH存储器时钟、USB模块时钟等系统时钟,配置基于MCG输出基准时钟的分频系数。SIM模块还用于控制外设时钟是否选通,打开使用模块时钟,关闭未使用模块时钟,这些时钟的门控,有利于降低芯片功耗。

但是对于SIM的编程却非常的简单,只要关注这样两组寄存器即可: SIM\_SCGCx和SIM\_CLKDIVx(x表示1-7的数字,不同封装的芯片略有差异)。

1. SIM\_SCGC(系统时钟门控System Clock Gating Control): 这一组寄存器控制外设模块时钟的开关。我们以SCGC4寄存器下面的UART0位举例说明,手册中是这样描述的:

| 10<br>UARTO | UART0 Clock Gate Control                              |  |  |  |  |  |  |

|-------------|-------------------------------------------------------|--|--|--|--|--|--|

| 0/1110      | This bit controls the clock gate to the UART0 module. |  |  |  |  |  |  |

|             | 0 Clock disabled                                      |  |  |  |  |  |  |

|             | 1 Clock enabled                                       |  |  |  |  |  |  |

图 140 SCGC4 寄存器中 UART0 位的定义

如果要开启或关闭UART0模块的时钟,只需用最简单的赋值操作对这个位进行操作即可。 对于其他模块的时钟开关,只要选定相对应的控制位,所有的位操作都是相同的。

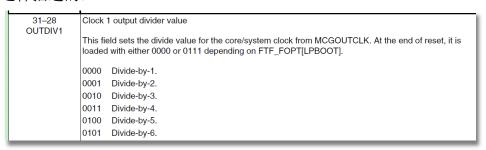

2. SIM\_CLKDIV(系统时钟分频System Clock Divider): 这一组寄存器控制MCG输出时钟后的分频因子,分配给内核、总线、Flash等。以CLKDIV1寄存器中的OUTDIV1位为例,手册中是这样描述的:

图 141 OUTDIV1 位的定义

可以看到这一位定义了MCGOUTCLK给内核时钟的分频,再参考一下前面的K22时钟分配图,直接赋值,也同样方便。如果使用"Processor Expert"工具,所有对这些控制位的赋值操作都可以通过图形化界面的选择来实现。

### 6.3.2 GPIO

GPIO是所有MCU软件最常使用的功能,对I/O口的编程本身并不复杂,只需要配置少数几个寄存器。

首先需要进行PinMux的设置。芯片在设计的时候,会把很多个功能集成在同一个物理管脚上,用户在使用的时候,需要进行设置。还是以K22为例,在手册的Signal Multiplexing and Signal Descriptions章节,会有一个表格详细地说明每个管脚的复用功能,如图 142所示。

| Pino       | ut          |            |                  |                    |           |           |                    |           |                   |           |      |          |                 |        |

|------------|-------------|------------|------------------|--------------------|-----------|-----------|--------------------|-----------|-------------------|-----------|------|----------|-----------------|--------|

| 121<br>BGA | 100<br>LQFP | 64<br>LQFP | 64<br>Map<br>Bga | Pin Name           | Default   | ALT0      | ALT1               | ALT2      | ALT3              | ALT4      | ALT5 | ALT6     | ALT7            | EzPort |

| E4         | 1           | 1          | <b>A</b> 1       | PTE0/<br>CLKOUT32K | ADC1_SE4a | ADC1_SE4a | PTE0/<br>CLKOUT32K | SPI1_PCS1 | UART1_TX          |           |      | I2C1_SDA | RTC_<br>CLKOUT  |        |

| E3         | 2           | 2          | B1               | PTE1/<br>LLWU_P0   | ADC1_SE5a | ADC1_SE5a | PTE1/<br>LLWU_P0   | SPI1_SOUT | UART1_RX          |           |      | I2C1_SCL | SPI1_SIN        |        |

| E2         | 3           | -          | -                | PTE2/<br>LLWU_P1   | ADC1_SE6a | ADC1_SE6a | PTE2/<br>LLWU_P1   | SPI1_SCK  | UART1_<br>CTS_b   |           |      |          |                 |        |

| F4         | 4           | -          | -                | PTE3               | ADC1_SE7a | ADC1_SE7a | PTE3               | SPI1_SIN  | UART1_<br>RTS_b   |           |      |          | SPI1_SOUT       |        |

| H7         | 5           | 1          | -                | PTE4/<br>LLWU_P2   | DISABLED  |           | PTE4/<br>LLWU_P2   | SPI1_PCS0 | LPUARTO_<br>TX    |           |      |          |                 |        |

| G4         | 6           | -          | -                | PTE5               | DISABLED  |           | PTE5               | SPI1_PCS2 | LPUARTO_<br>RX    |           |      | FTM3_CH0 |                 |        |

| F3         | 7           | -          | -                | PTE6               | DISABLED  |           | PTE6               | SPI1_PCS3 | LPUARTO_<br>CTS_b | I2S0_MCLK |      | FTM3_CH1 | USB_SOF_<br>OUT |        |

| E6         | 8           | 3          | C5               | VDD                | VDD       | VDD       |                    |           |                   |           |      |          |                 |        |

图 142 芯片的引脚复用

这个表格中,横向的ALT0-ALT7就是表示该管脚可以用来实现哪些功能,我们以PTE3(管脚标号4)为例,Default是ADC1\_SE7a,说明上电后,默认为ADC采样功能;从表格中看到,这个管脚还可以用作GPIO(PTE3)、SPI1的SIN或SOUT、UART1的RTS b等。

对PinMux的设置在Port Control寄存器中。Port Control是很多个寄存器组,命名方式为PORTx\_PCRn,其中x表示字母ABCDEF,对应PTA-PTE,表示端口A到端口E; n是数字,表示每一个Port包含的实际管脚。比如上文说的PTE3,就对应于PORTE\_PCR3寄存器,查手册,可以看到这个寄存器各bit的定义如图 143所示。

图 143 PTE3 的端口控制寄存器

下面详细说明其中各个控制或状态位的含义。

- ISF(Interrupt Status Flag):该管脚作为GPIO时,对应的中断标志位。

- IRQC(Interrupt Configuration):配置GPIO中断类型,比如上升/下降沿触发,电平0/1触发,触发使用DMA还是CPU中断。

- LK(Lock Register): 设置此寄存器的0~15位是否锁定。锁定后,这些位不能再修改,直到系统再次复位。

- MUX(Pin Mux Control):对应管脚的不同功能,总共3位来确定该管脚的功能是ALT0-ALT7中的哪一个。

- DSE(Drive Strength Enable):设置该IO管脚是否可输出大电流。

- ODE (Open Drain Enable):配置管脚是否开漏输出,0表示推挽输出,1表示开漏输出。

- PE(Pull Enable):配置是否使能内部上下拉电阻。

- PS (Pull Select): 0表示下拉,1表示上拉。

只要使用简单的赋值语句,给这些寄存器赋对应的值即可。本节重点讨论GPIO功能使用,当把管 脚配置成GPIO后,便可以对IO口进行操作。

GPIO寄存器根据端口A到E,分为GPIOx。在实际应用中,主要使用下面三组寄存器:

- GPIOx PDDR:设置该IO口的方向,0表示输入,1表示输出。

- GPIOx PDIR: 该管脚配置为输入时,这一位表示管脚上的输入逻辑。

- GPIOx PDOR: 该管脚配置为输出时,输出的逻辑,0为低电平,1为高电平。

这些寄存器的每一个bit对应于一个IO管脚,比如GPIOA\_PDDR[2]就对应PTA2管脚,对这些寄存器直接操作,就可以配置PTA2管脚的状态。

最后还有一点需要补充,用户在实际使用时,如果有部分管脚没有使用,建议配置为输出,并且输出低电平并接地。这样处理对EMC性能最好,当然如果要求不高的话,不接地悬空也是可以的。

## 6.3.3 ADC模块

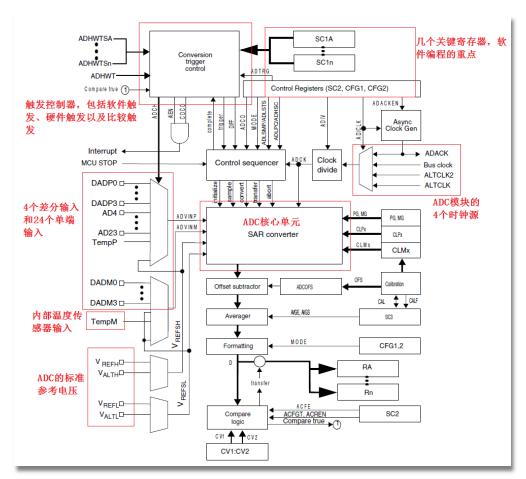

ADC转换也是用户常用的模块,这一小节主要介绍一下飞思卡尔Kinetis MCU中ADC模块。很多 Kinetis MCU片上集成了一个16位精度的逐次逼近ADC,支持单端和差分输入,此外还有硬件平均、校准等其他功能,能够满足基本的工业应用的需要。

图 144是ADC模块的系统框图,第一眼看上去有些复杂,但是用户不用担心,按照红线圈起来的几个重点部分划分,其实很容易理解。

图 144 ADC 模块框图

ADC模块本身比较复杂,涉及的功能也很多,由于篇幅限制这里不能一一详细讲解,本文的重点是几个关键的部分,让读者能够快速上手,利用ADC模块实现最基本的功能。

- 首先需要配置PinMux,把用来进行ADC采样的管脚,配置成对应的ADC功能。

- 其次需要知道ADC的触发模式,即在什么条件下触发ADC采样。Kinetis的ADC模块有两种触发方式,一种是硬件触发,MCU内部的其他模块(比如比较器、Timer等)和ADC有内部互联,满足指定条件就可无需CPU干预,直接触发ADC采样(比如Timer达到一个计数值)。另外一种是软件触发,只要对某一个寄存器写操作,就可以触发采样。对于触发方式的选择,可配置ADC SC2寄存器的ADTRG位。

如果要使用硬件触发方式,首先需要配置触发源,相应的控制位在SIM模块的SOPT寄存器中,在K22中是SIM\_SOPT7寄存器,里面有ADC1TRGSEL和ADC0TRGSEL位,对应于两个独立的ADC模块,ADC0和ADC1,如图 145所示。

图 145 ADC 触发源选择

对于触发源的配置,需要设置ADC\_SC1寄存器。有几个触发源,就会有几个SC1寄存器,从SC1A到SC1n,它们一一对应的。用户可以参考ADC模块框图最上面的部分。SC1寄存器包含ADC转换功能的控制位,以及相应的标志位,主要包括:

- COCO: 转换完成标志,为1说明当前转换已经完成。

- AIEN: 中断使能。

- DIFF: 是否启用差分模式, 0表示单端输入, 1表示差分输入。

- ADCH[4:0] 输入通道选择,选择使用哪一个引脚来采样数据,具体看手册引脚定义,该配置与差分模式也有关系。

而对于软件触发,只要SC1A寄存器的ADCH位不是全1,那么对SC1A寄存器的任意写操作,就可以触发一次ADC采样了。

软硬件触发的选择,取决于ADC SC2寄存器的ADTRG位。

在开始AD转换之前,除了触发方式和触发源的选择,还有一些其他的寄存器需要配置,主要是下面几个:

- CFG1寄存器,其中包括:

- ADIV[6:5]: 时钟分频,分别对应输入时钟的1/2/4/8分频。

- ADICLK[1:0]: ADC模块输入时钟选择,可以在总线时钟、异步时钟等时钟源中选择一个作为ADC模块的时钟输入。

- ADLPC: 低功耗设置,为1表示启用低功耗,牺牲采样率换取功耗。

- ADLSMP: 长/短采样时间设置,1表示长采样时间。

- CFG2寄存器,其中包括:

- ADHSC: 高速配置,如果输入时钟源频率很高,置1该位可获得更快的总转换时间。

- ADLSTS[1:0]: 长采样时间,当前面提到的ADLSMP=1,即选择了长采样时间时,该位设置具体添加几个时钟周期。

- SC2寄存器,其中包括:

- ADTRG: 软硬件触发设置,1表示硬件触发,0表示软件触发。

- DMAEN: DMA使能。

- SC3寄存器,其中包括:

- AVGE: 硬件平均,置1表示启用硬件平均。

- CAL: 置1开始校准, 在校准过程中会保持为1, 完成后自动清零。

总而言之,这些配置都是ADC的一些功能设置,能够利用采样时间,换取更好的精度或者功耗性能,具体怎么设置,需要根据实际需求。

除了上面这些功能以外,ADC还有很多其他的功能,比如比较触发、DMA搬运数据等,本文不再细讲,感兴趣的用户,可以自行查阅手册。

配置好了ADC模块,并且满足触发条件,ADC就会开始工作。当SC1n寄存器中的COCO位置1后,说明采样结束。此时的结果,会存放在ADC\_Rn寄存器中,n也表示触发源的个数,Rn寄存器的数量与SC1n一样,比如SC1B的结果存放在RB中。

ADC的详细主要功能和使用方法可以查阅手册,也可以参考飞思卡尔官方的示例代码。

当然用户也可以通过PE图形化的操作界面来配置ADC模块,这里就不再赘述。

# 6.3.4 UART模块

Kinetis的UART模块功能非常强大,支持硬件流量控制、红外、ISO7816、地址匹配等很多功能,作为面向初学者的起步文档,本文仍然着力于UART的基本功能,即数据的收发,让开发者能够快速上手,实现UART的基本功能。

Kinetis MCU一般有多个UART模块,这些模块可能会有一些差别,以100MHz的K22为例,如表 6 所示。需要注意的是,不同系列的MCU,如120M的K22,其模块硬件配置是有所不同的,用户还需仔细查阅用户手册的说明。

#### 表 6 UART 模块的差别

| UART 模块 | 是否支持 ISO7816 | FIFO 深度 | 模块时钟              | 最大波特率    | 低功耗支持 |

|---------|--------------|---------|-------------------|----------|-------|

| UART0   | 是            | 8       | 内核时钟,最大<br>100MHz | 6.25Mbps | 否     |

| UART1   | 是            | 1       | 内核时钟最,大<br>100MHz | 6.25Mbps | 否     |

| UART2   | 是            | 1       | 外设时钟最大,<br>50MHz  | 3.13Mbps | 否     |

| LPUART  | 否            | 无 FIFO  | 多时钟可选             | 6.25Mbps | 是     |

一些UART模块只能选取总线时钟,另一部可以自由配置,对于UART模块的时钟配置,需要看SIM这一章节,对应于SOPT寄存器。以K22为例,在SOPT2中,时钟的选择如图 146所示。

| 27–26<br>LPUARTSRC | LPUART clock source select                                                                                                         |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| El GAITTOTIO       | Selects the clock source for the LPUART transmit and receive clock.                                                                |  |  |  |  |  |

|                    | 00 Clock disabled 01 MCGFLLCLK, or MCGPLLCLK, or IRC48M clock as selected by SOPT2[PLLFLLSEL]. 10 OSCERCLK clock 11 MCGIRCLK clock |  |  |  |  |  |

图 146 UART 时钟源配置

可以分别选取内部、外部参考时钟,FLL\PLL时钟作为UART模块的时钟。不同时钟源会影响到 波特率的设置,同时在低功耗模式下,要确保时钟源没有关闭。

要使用UART模块完成最基本的数据收发,首先需要对UART进行初始化,配置通信的基本参数,几个关键点如下:

## • 波特率:

- UART BDH和UART BDL寄存器的SBR位,共12-bit表示一个波特率。

- UART C4寄存器, 里面的BRFA位, 5位表示对应的32分频。

- UART模块的时钟:参见SIM SOPT2寄存器的LPUARTSRC位。

- 波特率 = 模块时钟频率/(16 \* (SBR[12:0] + BRFD))

## • 数据帧格式:

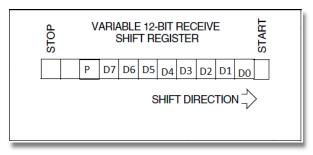

UART通信的数据帧格式如图 147所示:

图 147 UART 的帧格式

从图 147中可以看到, UART每帧的数据包括1个开始位, 若干个数据位, 紧接着是奇偶校验位, 最后是停止位。

用户需根据不同的使用需求,配置如下寄存器:

- UART C1: M位,选择8-bit还是9-bit数据位,1表示9-bit数据位。

- UART C1: PE位,置1使能奇偶校验。

- UART C1: PT位, 奇/偶选择, 1表示奇校验, 0表示偶校验。

当这些UART基本配置完成后,就可以开始收发数据了。还需要先使能UART收发器,这个操作在UART C2寄存器中,TE置1使能发送,RE置1使能接收。

收发器使能完毕后,如果是发送数据,则首先需要等待UART\_S1寄存器的TDRE位置1,这一位为1时表示目前可以发送数据,此时只要将待发数据写入UART\_D寄存器中即可完成发送。关于TDRE位是否置1,可以采用轮询的方式查询这一位;也可以配置UART\_C2中的TIE位为1来使能中断,一旦TDRE为1,会产生一个中断。

接收数据的过程与发送类似。收发器使能完毕后,如果有数据发送过来,UART模块会自动接收。如果UART\_S1寄存器的RDRF位置1,说明此时数据已经接收完毕,只要读取UART\_D寄存器即可获得刚才接收到的数据。关于RDRF位是否置1,也是同样可以采用轮询的方式去查询或者采用中断方式,对应的中断使能位是UART C2中的RIE。

这里还有一点需要说明,UART\_D寄存器只有8-bit,如果使用了9-bit数据帧,那么第9 bit的数据位于UART C3寄存器的T8或R8位。

UART的其他功能,比如FIFO的使用、接收唤醒、硬件流量控制等,用户可以自行查阅相关手册。 在本文后面介绍SDK的章节,还包括一个用SDK实现UART功能的例子,用户可以参考。

# 6.3.5 低功耗设置

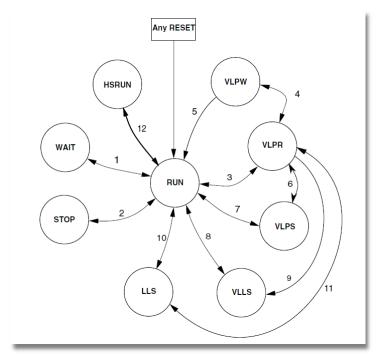

Kinetis系列MCU具备多种低功耗模式,用户可以在功耗和性能之间进行权衡。在说明MCU的低功耗模式之前,首先需要介绍一下ARM的内核。ARM Cortex M4的内核,包含了三种不同的工作模式,分别是Run,Sleep,以及Deep Sleep。其中:

• Run就是常规的运行模式,最大化性能:

- 在Sleep模式下,内核会停止工作,但是能响应中断;

- 在Deep Sleep模式下,内核会处于静态,停止响应中断。

Kinetis在ARM本身的模式上,通过对外设的不同控制,扩展出了13种不同的模式,主要介绍见表7。

## 表7低功耗模式说明

| 运行模式                                   | 描述                                                                                              | 对应 ARM 内核模式        | 常用的唤醒方法 | 典型的电流值  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------|--------------------|---------|---------|--|

| RUN,运行模式                               | 正常的运行模式                                                                                         | Run                | \       | 13.83mA |  |

| HSRUN,High<br>Speed Run,高速<br>运行模式     | 最高频率运行,最大化性能                                                                                    | Run                | \       | 23.6mA  |  |

| VLPR,Very Low<br>Power Run,低功<br>耗运行   | 降频运行,内核频率只有 4MHz,关掉低压检测功能;片上的电压调节器只输出刚刚足够的功率                                                    | Run                | \       | 0.61mA  |  |

| WAIT,等待模式                              | 内核进入 sleep 模式,但是外设模块可以正常工作;能够正常响应中断                                                             | Sleep              | 中断      | 4.4mA   |  |

| VLPW,Very Low<br>Power Wait,低功<br>耗等待  | 与 WAIT 模式类似,只是会降频运行,<br>关闭低电压检测                                                                 | Sleep              | 中断      | 0.382mA |  |

| STOP,停止模式                              | 芯片会进入静态状态,不响应中断,但可通过一些异步中断唤醒芯片;外设的时钟关掉,绝大多数外设会停止运行                                              | Deep Sleep         | 中断      | 0.27mA  |  |

| VLPS,低功耗停止                             | 与 STOP 类似,只是会降频运行,关闭<br>低压检测。 <b>能够让 ADC 运行和支持 I/O</b><br><b>中断的最低功耗模式。</b>                     | Deep Sleep         | 中断      | 4.5uA   |  |

| LLS3,Low Leakage<br>Stop 3,停止 3 模<br>式 | 内核时钟,系统时钟,总线时钟全部关掉。内部的逻辑、所有的 RAM 状态能够保持。                                                        | Deep Sleep         | 唤醒中断    | 2.6uA   |  |

| LLS2,Low Leakage<br>Stop 2,停止 2 模<br>式 | 与 LLS3 类似,但只保留 SRAM_U 的一部分。(CPU 内部逻辑保持的最低功耗模式,再往后唤醒相当于 CPU 复位)                                  | Deep Sleep         | 唤醒中断    | 2.4uA   |  |

| VLLS3                                  | 内部所有逻辑掉电,所有的 SRAM 状态<br>能够保持。                                                                   | Deep Sleep         | 低功耗唤醒复位 | 1.9uA   |  |

| VLLS2                                  | 在 VLLS3 的基础上,再关闭部分 SRAM (SRAM_L 的全部和 SRAM_U 的一部分)                                               | Deep Sleep 低功耗唤醒复位 |         | 1.7uA   |  |

| VLLS1                                  | 在 VLLS2 的基础上,所有的 SRAM 全部<br>掉电,只保留 32-Byte 的系统 register<br>file 和 32-Byte 的 VBAT register file。 | Deep Sleep         | 低功耗唤醒复位 | 0.73uA  |  |

| VLLS0                                  | 在 VLLS1 的基础上,再关闭 1kHz 的低功耗时钟。 <b>所有的低功耗模式,I/O</b> 口 <b>的状态都能保持</b>                              | Deep Sleep         | 低功耗唤醒复位 | 0.14uA  |  |

这里还需要说明一点,每个低功耗模式下的实际电流,与芯片温度、各个模块的使能情况相关,实际使用会有一些差异,本文只给出一些典型数值,具体的应用情况,请参考芯片技术手册。 这些低功耗模式之间不能随意切换,具体的转换图如图 148所示。

图 148 低功耗模式状态转换图

低功耗模式进入和退出的具体操作,请参阅参考手册的"System Mode Controller (SMC)"章节,此外还有很多细节上需要注意的地方,比如时钟模式设置,一些模块的状态等。本文建议初次接触飞思卡尔产品的用户在Freescale官方的参考代码基础上或者采用SDK进行低功耗模式的开发。

## 6.3.6 USB编程简介

USB协议本身比较复杂,详细介绍超出了本文的范畴。本节不会涉及复杂的USB功能开发细节,只是简单介绍一下对Kinetis MCU的USB应用开发,飞思卡尔能够提供哪些资源,以及怎样使用这些资源。

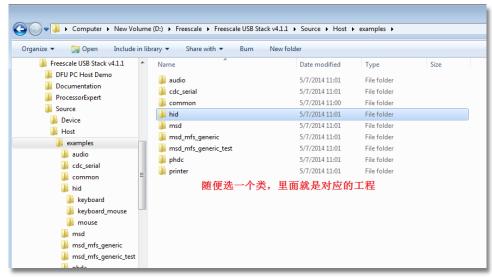

对于USB的应用,飞思卡尔提供了一个完整USB协议栈,目前最新正式版4.1.1,提供HID、HUB、CDC等所有常见类的支持,全面自持Device、Host、OTG三种方式,能很好的与Kinetis MCU配合。USB协议栈的下载链接如下:

http://www.freescale.com/zh-Hans/webapp/sps/site/prod\_summary.jsp?code=MEDICALUSB&uc=true&lang\_cd=zh-Hans

下载后安装即可。

飞思卡尔的USB协议栈提供了非常全面的例程,几乎所有的USB类都有若干个例程可以参考,这里强烈建议初学者先打开这些例程看看,跑跑对应的代码,熟悉一下协议栈。这些例程位于"协

议栈的"安装目录"→"Source"→"Device"或"Host"或"OTG"→"examples"目录下,如图 149所示。

图 149 打开 USB 协议栈工程

针对CodeWarrior、IAR、Keil的例程都是现成的,可直接导入,编译下载即可。

另外,安装目录下的Documentation文件夹里面,包含了USB协议栈使用的所有相关文档。这里建议先浏览一下USBHOSTUG、USBOTGUG和USBUG三个文档,分别介绍了Host、Device、OTG的使用,以及怎样建立自己的应用程序。关于协议栈的具体细节,限于篇幅,这里就不深入讨论了。

# 6.4 基于Kinetis SDK的开发

软件开发套件(SDK,Software Development Kit),由强大的外设驱动、协议栈、中间件和示例应用组成,旨在简化和加速基于所有Kinetis MCU的应用开发。现在推出的SDK是针对Kinetis MCU的,所以又称为KSDK。前面已经提到,SDK将整个软件进行分层,提供了各种功能丰富的函数,这些函数可直接对寄存器进行操作,用户不必自己去写对寄存器进行操作的代码,所以大大地节省了用户阅读手册的时间。

在使用SDK之前,首先需要完成两步的设置,分别是设置环境变量,以及在KDS中安装与SDK有关的eclipse插件。这两个操作的详细步骤,可参考本文档KSDK的下载与安装的内容。

SDK本身包含了大量的例程,这些例程涉及到了Kinetis各个模块的典型用法,对于初学者,建议 先导入例程进行初步的研究,对SDK整体上有一个大概的了解,例程存放于"SDK安装目录\demos"下面,直接导入编译运行即可。

图 150 SDK 的库文件

需要注意的是,在编译例程工程之前,用户应该先编译SDK的库。SDK库位于"SDK安装目录\lib\ksdk\_platform\_lib"目录中,库本身也是一个工程,导入后先进行编译,编译结束后,就可以编译例程了。SDK库的工程名ksdk platform lib,如图 150所示。

在SDK库文件的"platform"目录下,包含了该芯片所有能用到的功能模块。首先是clock目录,因为时钟管理由system services层提供支持,所以其中还包含了"system"目录,其中含有对时钟进行操作的所有函数,比如初始化、设置分频、MCG模式切换等,具体每个函数的实现,用户可参看代码。

对比gpio目录,可以看到有所不同的是其中包含了"common"、"drivers"、"hal"三个目录。其中drivers就是外设驱动层,hal就是硬件抽象层,里面同样包含了对GPIO进行操作的代码。

再看一下lptmr的工程文件,在其main函数中,包含了lptmr配置、初始化、开始计数这一系列功能的实现函数,都是调用驱动层的API来实现的,如图 151所示。

```

lptmr_demo.c 🗯 🖟 fsl_lptmr_d...

c fsl_port_hal.c c fsl_uart_hal.c k fsl_uart_hal.h c fsl_lptmr_d...

h f

int main (void)

gLPTMR_counter=0;

lptmr_user_config_t lptmrUserConfig = lptmr模块配置的结构体

.timerMode = klptmrTimerModeTimeCounter, /* Use LPTMR in Time Counter

.freeRunningEnable = false, /*When hit compare value, set counter back to zero */

.prescalerEnable = false, /* bypass prescaler */

.prescalerClockSource = kLptmrPrescalerClockSourceLpo, /* use 1kHz Low Power Clock */

.isInterruptEnabled = true

/* Initialize standard SDK demo application pins */

hardware_init();

对应

/* Configure the UART TX/RX pins */

configure_uart_pins(BOARD_DEBUG_UART_INSTANCE);

/" Call this function to initialize the console UART. This function

e use of STDIO functions (printf, scanf, etc.) *

dbg_uart_init();

printf("Low Power Timer Example\n\r");

* Initialize LPTMR */

LPTMR_DRV_Init(LPTMR_INSTANCE, &lptmrUserConfig, &gLPTMRState); 初始化

Set the timer period for 1 second "/

LPTMR_DRV_SetTimerPeriodUs(LPTMR_INSTANCE,1888888); 设置周期

Specify the callback function when a LPTMR interrupt occurs

LPTMR_DRV_InstallCallback(LPTMR_INSTANCE,lptmr_isr_callback);中断函数

Start counting */

LPTMR_DRV_Start(LPTMR_INSTANCE); 开始计数

printf("Started LPTMR\n\r");

/" Wait for LPTMR interrupt once every second "/

while(1)

{}

```

图 151 LPTMR 工程的 Main 函数调用

在lptmr的main函数中,调用了几个driver层的函数,这些driver层的函数,本身又会调用HAL层的函数,这里体现了SDK的分层结构。用户可以在lptmr的目录下查看各个函数的具体实现。

如果用户需要自己开发程序,可以根据实际需求,调用platform库中所有的HAL、Driver层的函数。

## 注意

不要同时调用不同层的函数。

下面以UART模块为例,通过调用驱动层函数来实现数据的收发。每个模块驱动的使用,都需要两个结构体变量,这两个结构体,一个完成对模块的配置,一个记录模块的状态,以UART为例,配置结构体定义如图 152, 里面定义了波特率、奇偶校验、数据帧长度等设置。

图 152 UART 模块配置结构体定义

状态结构体定义如图 153所示。

```

60⊖ typedef struct UartState {

uint8_t txFifoEntryCount;

/*!< Number of data word entries in TX FIFO. */

/*!< The buffer of data being sent.*/

/*!< The buffer of received data. */</pre>

const uint8_t * txBuff;

62

uint8 t * rxBuff;

63

/*!< The remaining number of bytes to be transmitted. */

64

volatile size_t txSize;

volatile size_t rxSize;

/*!< The remaining number of bytes to be received. */

/*!< True if there is an active transmit. */

volatile bool isTxBusy;

/*!< True if there is an active receive. */

volatile bool isRxBusy;

volatile bool isTxBlocking; /*!< True if transmit is blocking transaction. */</pre>

uart rx callback t rxCallback; /*!< Callback to invoke after receiving byte.*/

void * rxCallbackParam; /*!< Receive callback parameter pointer.*/</pre>

74 } uart_state_t;

```

图 153 UART 模块状态结构体定义

状态结构体中定义了当前UART模块运行时候的一些变量。

用户在使用UART模块时,需要首先定义这两个数据结构,然后就可以调用UART模块的初始化函数了,如图 154所示。

```

uart_state_t uartCom1_State; 定义状态结构体

59

uart_user_config_t uartConfig_user; 定义配置结构体

62

/* Configure the UART for 115200, 8 data bits, No parity, and one stop bit*/为配置结构体赋值

63

uartConfig user.baudRate = 115200;

64

uartConfig_user.bitCountPerChar = kUart8BitsPerChar;

65

uartConfig_user.parityMode = kUartParityDisabled;

66

uartConfig_user.stopBitCount = kUartOneStopBit;

67

68

UART DRV Init(FSL UARTCOM1, &uartCom1 State, &uartConfig user);调用初始化函数

69

```

图 154 UART 模块初始化

初始化函数有三个参数,第一个参数表示UART实体,一个芯片里面可能多个UART模块,用一个数字进行区分,比如0表示UART0;第二个和第三个参数就是前面定义的两个结构体。Driver层会根据这些参数,对UART模块进行初始化操作。初始化结束后,就可以开始进行数据的收发了,示例代码如图 155所示。

```

/* Write your local variable definition here */

uint8_t data[19] = {"\r\nHello World!\n\n\r"}; 特发送的数据

uart_state_t uartCom1_State;|

uart_user_config_t uartConfig_user;

/* Configure the UART for 115200, 8 data bits, No parity, and one stop bit*/

uartConfig_user.baudRate = 115200;

uartConfig_user.bitCountPerChar = kUart8BitsPerChar;

uartConfig_user.parityMode = kUartParityDisabled;

uartConfig_user.stopBitCount = kUartOneStopBit;

UART_DRV_Init(FSL_UARTCOM1, &uartCom1_State, &uartConfig_user);

WART_DRV_SendDataBlocking(FSL_UARTCOM1, data, 17,200);发送数据

```

图 155 UART 发送函数示例代码

在示例代码中,定义了一个数组"data[19]"来存放待发送数据,然后直接调用驱动中的发送函数 UART\_DRV\_SendDataBlocking()即可。数据的接收与发送类似,只是调用不同的函数。除了收发

函数,驱动层还提供了诸如反初始化、获取当前状态、终止发送等诸多函数,函数接口都不复杂,用户可以自行研究。

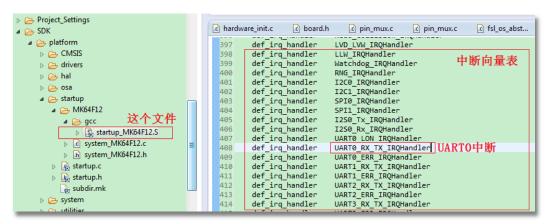

最后,还要再提一下SDK的中断使用。在启动代码中,会有一个startup\_MK64F12.s文件(不同型号的芯片后面数字会有差别),里面定义了中断向量表,如图 156所示。

图 156 SDK 的中断向量表

右边一栏中定义的就是每个中断的中断处理函数。在SDK中,将中断处理函数分成了两层来调用,图中定义的中断函数会再去调用驱动层提供的函数,清标志位、中断执行代码都是在驱动层完成的,如图 157所示。

```

* Passes instance to generic UART IRQ handler.

* Void UARTO_RX_TX_IRQHandler(void)实际的中断处理函数

* UART_DRV_IRQHandler(0);调用了驱动层的处理函数

* Name of the passes instance to generic UART IRQ handler.

```

图 157 中断的两级调用

如果用户不需要驱动层提供的API,想自己编写中断处理函数,只要进行简单的代码修改即可。 除了UART模块,其他模块驱动的调用与UART类似,限于篇幅,本文不一一举例。

用户在实际中编写自己的程序时,对某些函数的API和用法存在疑问时,可以参考demos目录下 SDK自带的例程,仿照例程使用。SDK提供的例程基本上能够涵盖所有的模块。

同时,doc目录下还包含了很多的文档,建议先阅读user guide,里面有一些最基本的使用说明,以及快速上手指南。更详细的每个函数细节描述,请参考文档 "SDK API Reference Manual"。

# 6.5 怎样移植客户的应用

在很多情况下,开发者已经有了自己的一套应用代码,或者有基于其他MCU的代码,那么如何将 其移至到Kinetis上面的呢?本小节将会从主要的方面给出一些基本的建议,并以KDS环境为例。

对于代码的移植,首先需要建立一个新的工程,并且在工程建立好之后,需要添加所有的C文件和h文件到相应的目录下,这两步较为简单,具体过程也可以参考介绍KDS的章节。有一点要注

意,在建立工程的时候,一定要选择对应的芯片,同时推荐使用PE工具,因为PE能提供一套非常完善的初始化代码,减少移植的工作量。源代码文件全部添加完成后,就可以调用里面的函数了。

其次需要正确配置时钟,不同开发板的时钟源是不一样的。配置时钟的代码在"CPU.c"或者"芯片名字.c(例如MK64XXX.c)"文件中,里面有对MCG、SIM\_CLKDIV等寄存器的操作,用户需要根据自己的实际情况来进行配置。当然这一步也可以直接采用PE来配置。

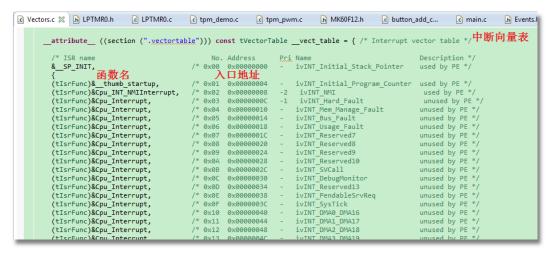

接下来需要设置中断向量表,在KDS中的Vectors.c文件里有一个指针数组,用来定义所有的中断向量的入口,如图 158所示。

图 158 修改中断向量表

用户需按照实际需求,将函数名改成实际使用的中断函数名。具体的中断向量号及入口地址,可以查阅芯片手册。

除了上面这些,用户还要按照目标板的需求,修改PinMux,将管脚配置成对应的功能,具体请参考本文的前一章节,GPIO部分。

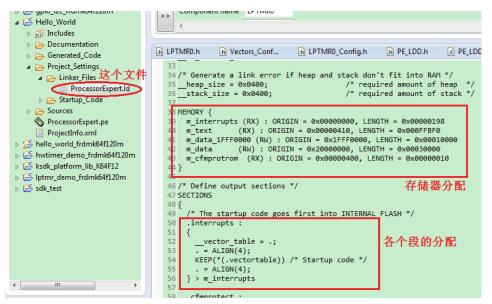

此外,还需要修改memory map,因为芯片的地址空间可能不同。比如原程序在1MB Flash的MCU上运行,那么移植目标芯片只有512KB,就需要注意合理的分配地址空间,确保地址不会溢出,以免程序跑飞。

最后,还需要修改Linker文件,来分配存储器空间的使用。在工程目录下,会有一个.ld文件,一般名字为芯片名(例如K64FN1Mxxx12.ld),如果之前的代码对地址分配有特殊需求,用户可在这里进行配置,如图 159所示。

图 159 Linker 文件修改

关于Linker文件的具体语法,请参考文档AN4498。此文档可以在Freescale官网搜索到。

How to Reach Us:

Home Page:

freescale.com

Web Support:

freescale.com/support

本文档中的信息仅供系统和软件实施方使用 Freescale 产品。本文并未明示或者暗示授予利用本文档信息进行设计或者加工集成电路的版权许可。Freescale 保留对此处任何产品进行更改的权利,恕不另行通知。

Freescale 对其产品在任何特定用途方面的适用性不做任何担保、表示或保证,也不承担因为应用程序或者使用产品或电路所产生的任何责任,明确拒绝承担包括但不局限于后果性的或附带性的损害在内的所有责任。Freescale 的数据表和/或规格中所提供的"典型"参数在不同应用中可能并且确实不同,实际性能会随时间而有所变化。所有运行参数,包括"经典值"在内,必须经由客户的技术专家对每个客户的应用程序进行验证。Freescale 未转让与其专利权及其他权利相关的许可。Freescale 销售产品时遵循以下网址中包含的标准销售参数和条件,freescale com/SalesTermsandConditions

条款和条件: freescale.com/SalesTermsandConditions.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2014 Freescale Semiconductor, Inc.